Template:Syscon pinout BGA 200 pads: Difference between revisions

Jump to navigation

Jump to search

mNo edit summary |

m (MK = Master clocK ?) |

||

| (2 intermediate revisions by the same user not shown) | |||

| Line 2: | Line 2: | ||

<span style="font-size:175%; font-family:Times New Roman;">Pinout</span> | <span style="font-size:175%; font-family:Times New Roman;">Pinout</span> | ||

---- | ---- | ||

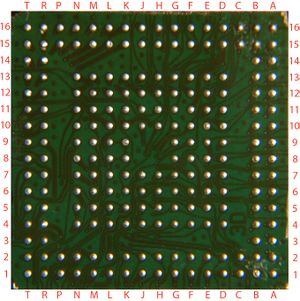

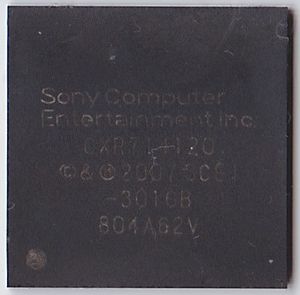

<div style="float:right">[[File:CXR713120-201GB-bottom.JPG| | <div style="float:right">[[File:CXR713120-201GB-bottom.JPG|300px|thumbnail|right|[[Mullion]] syscons, bottom view<br>With pad A1 mark at south-east corner]]<br>[[File:CXR714120-301GB - Top.jpg|300px|thumbnail|right|[[Mullion]] syscon, top view<br>With pad A1 mark at south-west corner]]</div> | ||

<div style="overflow:auto; <includeonly>height:800px;</includeonly>"> | <div style="overflow:auto; <includeonly>height:800px;</includeonly>"> | ||

| Line 116: | Line 116: | ||

| M9 || BUZZER || | | M9 || BUZZER || | ||

|- | |- | ||

| N9 || SW_PWM || | | N9 || SW_PWM || Unknown output ? (connected to the [[Switch boards|Switch board]]) | ||

|- | |- | ||

| M8 || FANPWM1 || | | M8 || FANPWM1 || Secondary fan output (non-retail PS3 models only) | ||

|- | |- | ||

| N8 || FANPWM0 || | | N8 || FANPWM0 || Primary fan output (all PS3 models) | ||

|- | |- | ||

| E10 || MUL_CHKSTP_OUT || rowspan="8" | Port F || | | E10 || MUL_CHKSTP_OUT || rowspan="8" | Port F || | ||

| Line 384: | Line 384: | ||

| R15 || HDMI_I2C_SDA || | | R15 || HDMI_I2C_SDA || | ||

|- | |- | ||

| D1 || MK_I2C_SCL || rowspan="10" | Port O | | D1 || MK_I2C_SCL || rowspan="10" | Port O || Connected to clock generator (IC5001 pin #46 on [[COK-001]]) | ||

|- | |- | ||

| C1 || MK_I2C_SDA || | | C1 || MK_I2C_SDA || Connected to clock generator (IC5001 pin #47 on [[COK-001]]) | ||

|- | |- | ||

| G4 || PO7 || | | G4 || PO7 || | ||

Revision as of 02:35, 5 December 2021

Pinout

| Pad# | Name | Port | Description |

|---|---|---|---|

| T2 | BE_INT | Port M Cell Control Line |

|

| R1 | PM7 | ||

| R2 | PM6 | ||

| P1 | BE_POWGOOD | ||

| P2 | BE_RESET | ||

| N1 | BE_SPI_CLK | Cell SPI Bus | |

| N2 | BE_SPI_DO | ||

| M1 | BE_SPI_DI | ||

| M2 | BE_SPI_CS | ||

| L4 | PL8 | Port N | unused |

| L5 | PL7 | ||

| K4 | PL6 | ||

| K5 | PL5 | ||

| J4 | PL4 | ||

| J5 | PL3 | ||

| H4 | PL2 | ||

| H5 | PL1 | ||

| H6 | PL0 | ||

| A8 | SB_SPI_CLK | Port K | Southbridge SPI Bus |

| B8 | SB_SPI_DO | ||

| A9 | SB_SPI_DI | ||

| B9 | SB_SPI_CS | ||

| A10 | DVE_I2C_SCL | ||

| B10 | DVE_I2C_SDA | ||

| A11 | ACDC_STBY | ||

| B11 | PK0 | ||

| B5 | PJ7 | Port J | |

| A5 | DISC_OUT12_SW | ||

| B2 | DISC_OUT8_SW | ||

| A2 | DISC_IN | ||

| B3 | SW_10 | ||

| A3 | SW_0 | ||

| B4 | SW_8_B | ||

| A4 | SW_8_C | ||

| L16 | SW_PCI | Port I | |

| L15 | DISC_CHUCK | ||

| M16 | DISC_PHOT_LED | ||

| M15 | SW_2 | ||

| N16 | DIAG_MODE | ||

| N15 | BACKUP_MODE | ||

| E6 | HDMI_INT | Port H | |

| D6 | VD_CECI0 | ||

| E7 | PH5 | ||

| D7 | RS_POW_FAIL | ||

| E8 | MUL_CHKSTP_IN | ||

| D8 | MUL_TRG_IN | ||

| E9 | SYS_THR_ALRT | ||

| D9 | SB_INT | ||

| M11 | SW_ATA | Port G | |

| N11 | SW_4_A | ||

| M10 | XDR_FET_VREF | ||

| N10 | XDR_FET_SCK | ||

| M9 | BUZZER | ||

| N9 | SW_PWM | Unknown output ? (connected to the Switch board) | |

| M8 | FANPWM1 | Secondary fan output (non-retail PS3 models only) | |

| N8 | FANPWM0 | Primary fan output (all PS3 models) | |

| E10 | MUL_CHKSTP_OUT | Port F | |

| D10 | MUL_TAG_OUT | ||

| E11 | SB_CGRESET | ||

| D11 | SB_RESET | ||

| E12 | BT_WAKEON | ||

| D12 | BE_VCS_1.25_ON | ||

| E13 | BE_VCS_1.30_ON | ||

| D13 | SW_1A | ||

| A12 | EJECT_SW | Port E | |

| B12 | POW_SW | ||

| A13 | SB_EBUS_RESET | ||

| B13 | SB_EBUS_BRDY | ||

| A14 | PE3 | ||

| B14 | VD_CECI1 | ||

| A15 | BE_POW_FAIL | ||

| B15 | POW_FAIL | ||

| F13 | SW_5_B | Port D | |

| F12 | MK_EN | ||

| G13 | BEVRM_VID5 | ||

| G12 | BEVRM_VID4 | ||

| H13 | BEVRM_VID3 | ||

| H12 | BEVRM_VID2 | ||

| J13 | BEVRM_VID1 | ||

| J12 | BEVRM_VID0 | ||

| K13 | SW_HDD | Port C | |

| K12 | I2CBUS_EN | ||

| L13 | RSXVRM_VID5 | ||

| L12 | RSXVRM_VID4 | ||

| M13 | RSXVRM_VID3 | ||

| M12 | RSXVRM_VID2 | ||

| N13 | RSXVRM_VID1 | ||

| N12 | RSXVRM_VID0 | ||

| T15 | SW_8_A | Port B | |

| R14 | SW_7_A | ||

| T14 | SW_6 | ||

| R13 | SW_1_B | ||

| T13 | SW_4_B | ||

| R12 | SW_3 | ||

| T12 | VD_CECO1 | ||

| R11 | VD_CECO0 | ||

| N7 | STBY_LED | Port A | |

| M7 | POW_LED | ||

| N6 | AUDIO_MUTE | ||

| M6 | SW_7_B | ||

| N5 | BT_RESET | ||

| M5 | GBE_RESET | ||

| N4 | SW_5_A | ||

| M4 | SW_9 | ||

| J16 | RBB | EEPROM Interface | |

| K16 | PI7 | ||

| J15 | WCB | ||

| K15 | PI6 | ||

| E16 | SKB | ||

| E15 | PP3 | ||

| G16 | DI | ||

| G15 | PP2 | ||

| H16 | DO | ||

| H15 | PP1 | ||

| F16 | CSB | ||

| F15 | PP0 | ||

| H11 | TESTMODE | Reset & Clock | |

| B16 | OSCOUT | ||

| C16 | OSCIN | ||

| D16 | 32KOUT | ||

| D15 | 32KIN | ||

| T5 | EXTAL | ||

| T4 | XTAL | ||

| T7 | XXTALO | ||

| J11 | RST | ||

| R4 | AVSUO | Power Port | Ground |

| R5 | AVDUO | +3.3v | |

| G6 | AVSS | Ground | |

| C2 | AVREF2 | Ground | |

| B1 | AVREF1 | +3.3v | |

| F7 | AVDD | +3.3v | |

| K11 | VSSF | Ground | |

| K6 | VSSF | Ground | |

| L6 | VDDF | +3.3v | |

| G7 | VSS | Ground | |

| G8 | |||

| G10 | |||

| T6 | |||

| R6 | |||

| T3 | |||

| L1 | |||

| E1 | |||

| C15 | VSSep | EEPROM Ground | |

| G11 | VDDep | EEPROM Power +3.3v | |

| F11 | VDDbat | +battery | |

| H7 | DVDD | +1.8v | |

| J10 | |||

| K10 | |||

| L10 | |||

| L11 | |||

| R7 | |||

| J7 | |||

| F8 | VDD3 | +3.3v | |

| F10 | |||

| H10 | |||

| J6 | |||

| F6 | |||

| D2 | VDD2 | +1.5V_RSX_VDDIO | |

| R3 | VDD1 | +1.2V_MC2_VDDIO | |

| L2 | VDD0 | +1.2V_MC2_VDDIO | |

| A16 | NC | ||

| T16 | |||

| T1 | |||

| A1 | |||

| G9 | |||

| F9 | |||

| L8 | JRTCK | JTAG Interface | |

| K8 | JTCK | ||

| K9 | JTDO | ||

| L9 | JTMS | ||

| K7 | JTDI | ||

| L7 | JNTAST | ||

| A6 | PR3 | Port R | |

| B6 | MC_P_OFF_REQ | ||

| A7 | MC_ALIVE | ||

| B7 | MC_RESERVED1 | ||

| R10 | RMC_IN | Port Q | |

| T11 | PQ5 | ||

| T10 | PQ4 | ||

| T8 | THR_I2C_SCL | ||

| T9 | THR_I2C_SDA | ||

| R9 | PQ1 | ||

| R8 | RSX_FBVDD_SEL | ||

| P16 | UART0_TxD | Port P | Serial Transmit |

| P15 | UART0_RxD | Serial Receive | |

| R16 | HDMI_I2C_SCL | ||

| R15 | HDMI_I2C_SDA | ||

| D1 | MK_I2C_SCL | Port O | Connected to clock generator (IC5001 pin #46 on COK-001) |

| C1 | MK_I2C_SDA | Connected to clock generator (IC5001 pin #47 on COK-001) | |

| G4 | PO7 | ||

| F4 | HDMI_RST0 | ||

| G5 | PO5 | ||

| F5 | DISC_IN_MECHA | ||

| E4 | EJECT_MECHA | ||

| D4 | XDR_FET_RST | ||

| E5 | GX_VSRST | ||

| D5 | XCG_EN | ||

| K2 | VD_VINT1 | Port N | |

| K1 | VD_VINT0 | ||

| J2 | RSX_INT | ||

| J1 | RSX_FLDO | ||

| H2 | PN6 | ||

| H1 | PN5 | ||

| G2 | RSX_RESET | ||

| G1 | RSX_SPI_CLK | RSX SPI Bus | |

| F2 | RSX_SPI_DO | ||

| F1 | RSX_SPI_DI | ||

| E2 | RSX_SPI_CS | ||