MB86C311B: Difference between revisions

Jump to navigation

Jump to search

mNo edit summary |

mNo edit summary |

||

| Line 17: | Line 17: | ||

=== Pinout === | === Pinout === | ||

<div style="float:right">[[File:MB86C311B Pinout.png|200px|thumb|left|MB86C311B Pinout]]</div> | <div style="float:right">[[File:MB86C311B Pinout.png|200px|thumb|left|Fujitsu [[MB86C311B]] USB 3.0 / SATA bridge - Pinout]]</div> | ||

{| border="1" cellspacing="0" cellpadding="5" border="#999" class="wikitable" style="border:1px solid #999; border-collapse: collapse;" | {| border="1" cellspacing="0" cellpadding="5" border="#999" class="wikitable" style="border:1px solid #999; border-collapse: collapse;" | ||

|- bgcolor="#cccccc" | |- bgcolor="#cccccc" | ||

Revision as of 01:55, 31 May 2015

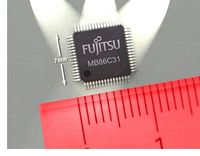

MB86C311B

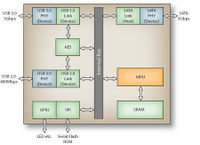

USB 3.0 / SATA bridge LSI

ARM Powered, contains Cortex M3 MCU.

The submodel [B] does not have hardware AES-XTS support

Is attached to an SPI Flash chip. Dump: http://www.psdevwiki.com/ps4/files/FlashDump/usb-bridge.bin

http://pdf.dzsc.com/99999/20101029175627721.pdf

http://www.fujitsu.com/downloads/MICRO/fma/pdf/MB86C31_FS_082010.pdf

Pinout

Fujitsu MB86C311B USB 3.0 / SATA bridge - Pinout

| Pin | Pin name | Description |

|---|---|---|

| 1 | ST_VDU | |

| 2 | ST_VDP | |

| 3 | ST_VDU | |

| 4 | ST_VDN | |

| 5 | ST_RXP | |

| 6 | ST_RXM | |

| 7 | ST_VDN | |

| 8 | ST_TXM | |

| 9 | ST_TXP | |

| 10 | PLLVDD | |

| 11 | PTST | |

| 12 | TMODE[2] | |

| 13 | VDDE | |

| 14 | TMODE[1] | |

| 15 | TMODE[0] | |

| 16 | SYSRST_X | |

| 17 | SCEN_X2 / GPIO[5] | |

| 18 | VDDI | |

| 19 | GPIO[4] | |

| 20 | GPIO[3] | |

| 21 | SD / NMSEL / GPIO[2] | |

| 22 | VDDE | |

| 23 | SCK / GPIO[1] | |

| 24 | SCEN_X1 / GPIO[0] | |

| 25 | IRQ / SCEN_X4 / GPIO[8] | |

| 26 | VBUS | |

| 27 | GPIO[7] | |

| 28 | SCEN_X3 / GPIO[6] | |

| 29 | VDDI | |

| 30 | U2_AVDF2 | |

| 31 | U2_HSDM | |

| 32 | U2_HSDP | |

| 33 | U2_AVDF1 | |

| 34 | U2_EXT12K | |

| 35 | U2_AVDF1 | |

| 36 | U2_AVDP | |

| 37 | VDDI | |

| 38 | SS_TXM | |

| 39 | SS_TXP | |

| 40 | SS_VDN | |

| 41 | SS_RXM | |

| 42 | SS_RXP | |

| 43 | SS_VDU | |

| 44 | SS_VDU | |

| 45 | VDDI | |

| 46 | SYS_XO | |

| 47 | SYS_XI | |

| 48 | VDDI |

| ||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||