Template:CELL pad layout 90nm: Difference between revisions

Jump to navigation

Jump to search

mNo edit summary |

No edit summary |

||

| (187 intermediate revisions by the same user not shown) | |||

| Line 1: | Line 1: | ||

<br style="clear: both;" /> | {{#ifeq:{{{raw|}}}|yes|<!-- if raw=yes dont display extras-->|<!--else--> | ||

<includeonly><br style="clear: both;" /> | |||

<span style="font-size:175%; font-family:Times New Roman;">Pinout</span> | <span style="font-size:175%; font-family:Times New Roman;">Pinout</span> | ||

---- | ---- | ||

<div style="float:right">[[File:CELL-GRID-bw- | </includeonly> | ||

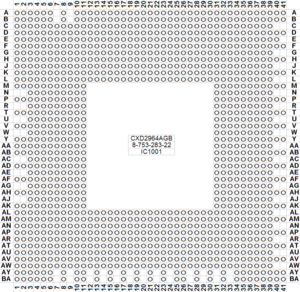

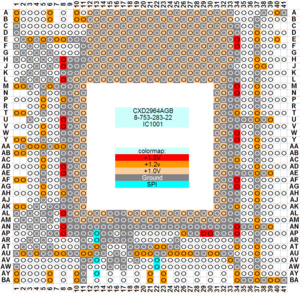

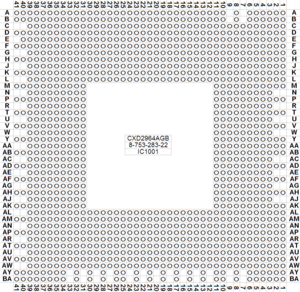

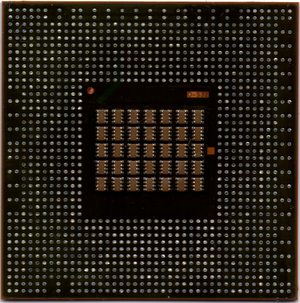

<div style="float:right">[[File:CELL-GRID-bw-pcbview.png|300px|thumb|left|CELL BE, padlayout<br>PCB view facing BGA<br>A1 marker:northwest/topleft]]<br>[[File:CELL-GRID-color-vcc-gnd-spi-pcbview.png|300px|thumb|left|CELL BE, padlayout<br>PCB view facing BGA<br>A1 marker:northwest/topleft]]<br>[[File:CELL-GRID-bw-cpu-bottomside.png|300px|thumb|left|CELL BE, padlayout<br>CPU view facing BGA<br>A1 marker:northeast/topright]]<br>[[File:Cell 90nm (1200dpi scan).bmp|300px|thumb|left|CELL 90nm pad layout (CELL view)<br>Pad A1 at bottom-left corner]]</div> | |||

<div style="overflow:auto; <includeonly>height:1200px;</includeonly>"> | |||

}} | |||

{| class="wikitable mw-datatable sortable" style="width:100%; line-height:1em; font-size:0.9em" | |||

{| class="wikitable mw-datatable" style="width:100%" | |+{{captionlinks|CELL pad layout 90nm}} | ||

|+ {{captionlinks|CELL pad layout | ! Pad !! colspan="2" | Name !! style="padding:1px" | Type !! Description | ||

! colspan="3" | A | |- | ||

! style="border-top:hidden; background-position:50%" | !! style="padding-right:0px" | Internal !! style="padding-right:0px" | External !! style="border-top:hidden; background-position:50%" | !! style="border-top:hidden; background-position:50%" | | |||

|- | |||

| data-sort-value="0A01" | A1 || {{cellcolors|#d53|#fff}} YC_VDDIO || +1.2V_YC_RC_VDDIO || {{pin}} || data-sort-value="Z1.2V_YC" | Connected to [https://www.digikey.com/en/products/detail/vishay-siliconix/SUD40N02-08-E3/2623039 Vishay Siliconix SUD40N02-08-E3] pin 3 | |||

|- | |||

| data-sort-value="0A02" | A2 || Y0_DQ1N_5 || Y0_XDR0_DQN10 || {{pino}} || Connected to [[RAM|XDR DRAM]] Y0_XDR0 (first chip) pad <abbr title="Unknown">UNK</abbr> | |||

|- | |||

| data-sort-value="0A03" | A3 || Y0_DQ1N_2 || data-sort-value="Y0_XDR0_DQN06" | Y0_XDR0_DQN6 || {{pino}} || Connected to [[RAM|XDR DRAM]] Y0_XDR0 (first chip) pad <abbr title="Unknown">UNK</abbr> | |||

|- | |||

| data-sort-value="0A04" | A4 || Y0_DQ0N_6 || Y0_XDR0_DQN14 || {{pino}} || Connected to [[RAM|XDR DRAM]] Y0_XDR0 (first chip) pad <abbr title="Unknown">UNK</abbr> | |||

|- | |||

| data-sort-value="0A05" | A5 || Y0_DQ0N_4 || data-sort-value="Y0_XDR0_DQN02" | Y0_XDR0_DQN2 || {{pino}} || Connected to [[RAM|XDR DRAM]] Y0_XDR0 (first chip) pad <abbr title="Unknown">UNK</abbr> | |||

|- | |||

| data-sort-value="0A06" | A6 || {{cellcolors|#d53|#fff}} YC_VDDIO || +1.2V_YC_RC_VDDIO || {{pin}} || data-sort-value="Z1.2V_YC" | Connected to [https://www.digikey.com/en/products/detail/vishay-siliconix/SUD40N02-08-E3/2623039 Vishay Siliconix SUD40N02-08-E3] pin 3 | |||

|- | |||

| data-sort-value="0A07" | A7 || data-sort-value="ZZZ" {{cellcolors|#eee|#888}} N/A || data-sort-value="ZZZ" {{cellcolors|#eee|#888}} N/A || data-sort-value="ZZZ" {{cellcolors|#eee|#888}} N/A || data-sort-value="ZZZ" {{cellcolors||#888}} Missing pad | |||

|- | |||

| data-sort-value="0A08" | A8 || Y0_DQ0N_1 || Y0_XDR1_DQN14 || {{pino}} || Connected to [[RAM|XDR DRAM]] Y0_XDR1 (second chip) pad <abbr title="Unknown">UNK</abbr> | |||

|- | |||

| data-sort-value="0A09" | A9 || data-sort-value="ZZZ" {{cellcolors|#eee|#888}} N/A || data-sort-value="ZZZ" {{cellcolors|#eee|#888}} N/A || data-sort-value="ZZZ" {{cellcolors|#eee|#888}} N/A || data-sort-value="ZZZ" {{cellcolors||#888}} Missing pad | |||

|- | |||

| data-sort-value="0A10" | A10 || {{cellcolors|#d53|#fff}} YC_VDDIO || +1.2V_YC_RC_VDDIO || {{pin}} || data-sort-value="Z1.2V_YC" | Connected to [https://www.digikey.com/en/products/detail/vishay-siliconix/SUD40N02-08-E3/2623039 Vishay Siliconix SUD40N02-08-E3] pin 3 | |||

|- | |||

| data-sort-value="0A11" | A11 || Y0_DQ0_RLOAD || BE_Y0_DQ0_RLOAD || {{pini}} || Resistor 49.9 ohms to +1.2V_YC_RC_VDDIO | |||

|- | |||

| data-sort-value="0A12" | A12 || {{cellcolors|#f93|#fff}} VDD || +1.0V_BE_VDDC || {{pin}} || data-sort-value="Z1.0V" | Connected to [[Regulators#iPowIR_IP2003ATRPBF_.2840A_Synchronous_Buck_Multiphase_Optimized_LGA_Power_Block.29|iPowIR IP2003ATRPBF]] (3 units) pin 6 (Vsw) through NEC/TOKIN proadlizers | |||

|- | |||

| data-sort-value="0A13" | A13 || {{cellcolors|#333|#fff}} GND || GND || {{pin}} || data-sort-value="ZGND" {{cellcolors||#888}} Ground | |||

|- | |||

| data-sort-value="0A14" | A14 || {{cellcolors|#f93|#fff}} VDD || +1.0V_BE_VDDC || {{pin}} || data-sort-value="Z1.0V" | Connected to [[Regulators#iPowIR_IP2003ATRPBF_.2840A_Synchronous_Buck_Multiphase_Optimized_LGA_Power_Block.29|iPowIR IP2003ATRPBF]] (3 units) pin 6 (Vsw) through NEC/TOKIN proadlizers | |||

|- | |||

| data-sort-value="0A15" | A15 || {{cellcolors|#333|#fff}} GND || GND || {{pin}} || data-sort-value="ZGND" {{cellcolors||#888}} Ground | |||

|- | |||

| data-sort-value="0A16" | A16 || {{cellcolors|#f93|#fff}} VDD || +1.0V_BE_VDDC || {{pin}} || data-sort-value="Z1.0V" | Connected to [[Regulators#iPowIR_IP2003ATRPBF_.2840A_Synchronous_Buck_Multiphase_Optimized_LGA_Power_Block.29|iPowIR IP2003ATRPBF]] (3 units) pin 6 (Vsw) through NEC/TOKIN proadlizers | |||

|- | |||

| data-sort-value="0A17" | A17 || {{cellcolors|#333|#fff}} GND || GND || {{pin}} || data-sort-value="ZGND" {{cellcolors||#888}} Ground | |||

|- | |||

| data-sort-value="0A18" | A18 || {{cellcolors|#f93|#fff}} VDD || +1.0V_BE_VDDC || {{pin}} || data-sort-value="Z1.0V" | Connected to [[Regulators#iPowIR_IP2003ATRPBF_.2840A_Synchronous_Buck_Multiphase_Optimized_LGA_Power_Block.29|iPowIR IP2003ATRPBF]] (3 units) pin 6 (Vsw) through NEC/TOKIN proadlizers | |||

|- | |||

| data-sort-value="0A19" | A19 || {{cellcolors|#333|#fff}} GND || GND || {{pin}} || data-sort-value="ZGND" {{cellcolors||#888}} Ground | |||

|- | |||

| data-sort-value="0A20" | A20 || {{cellcolors|#f93|#fff}} VDD || +1.0V_BE_VDDC || {{pin}} || data-sort-value="Z1.0V" | Connected to [[Regulators#iPowIR_IP2003ATRPBF_.2840A_Synchronous_Buck_Multiphase_Optimized_LGA_Power_Block.29|iPowIR IP2003ATRPBF]] (3 units) pin 6 (Vsw) through NEC/TOKIN proadlizers | |||

|- | |||

| data-sort-value="0A21" | A21 || {{cellcolors|#333|#fff}} GND || GND || {{pin}} || data-sort-value="ZGND" {{cellcolors||#888}} Ground | |||

|- | |||

| data-sort-value="0A22" | A22 || {{cellcolors|#f93|#fff}} VDD || +1.0V_BE_VDDC || {{pin}} || data-sort-value="Z1.0V" | Connected to [[Regulators#iPowIR_IP2003ATRPBF_.2840A_Synchronous_Buck_Multiphase_Optimized_LGA_Power_Block.29|iPowIR IP2003ATRPBF]] (3 units) pin 6 (Vsw) through NEC/TOKIN proadlizers | |||

|- | |||

| data-sort-value="0A23" | A23 || {{cellcolors|#333|#fff}} GND || GND || {{pin}} || data-sort-value="ZGND" {{cellcolors||#888}} Ground | |||

|- | |||

| data-sort-value="0A24" | A24 || {{cellcolors|#f93|#fff}} VDD || +1.0V_BE_VDDC || {{pin}} || data-sort-value="Z1.0V" | Connected to [[Regulators#iPowIR_IP2003ATRPBF_.2840A_Synchronous_Buck_Multiphase_Optimized_LGA_Power_Block.29|iPowIR IP2003ATRPBF]] (3 units) pin 6 (Vsw) through NEC/TOKIN proadlizers | |||

|- | |- | ||

| data-sort-value="0A25" | A25 || {{cellcolors|#333|#fff}} GND || GND || {{pin}} || data-sort-value="ZGND" {{cellcolors||#888}} Ground | |||

|- | |- | ||

| | | data-sort-value="0A26" | A26 || {{cellcolors|#f93|#fff}} VDD || +1.0V_BE_VDDC || {{pin}} || data-sort-value="Z1.0V" | Connected to [[Regulators#iPowIR_IP2003ATRPBF_.2840A_Synchronous_Buck_Multiphase_Optimized_LGA_Power_Block.29|iPowIR IP2003ATRPBF]] (3 units) pin 6 (Vsw) through NEC/TOKIN proadlizers | ||

|- | |- | ||

| | | data-sort-value="0A27" | A27 || {{cellcolors|#333|#fff}} GND || GND || {{pin}} || data-sort-value="ZGND" {{cellcolors||#888}} Ground | ||

|- | |- | ||

| | | data-sort-value="0A28" | A28 || {{cellcolors|#f93|#fff}} VDD || +1.0V_BE_VDDC || {{pin}} || data-sort-value="Z1.0V" | Connected to [[Regulators#iPowIR_IP2003ATRPBF_.2840A_Synchronous_Buck_Multiphase_Optimized_LGA_Power_Block.29|iPowIR IP2003ATRPBF]] (3 units) pin 6 (Vsw) through NEC/TOKIN proadlizers | ||

|- | |- | ||

| | | data-sort-value="0A29" | A29 || {{cellcolors|#333|#fff}} GND || GND || {{pin}} || data-sort-value="ZGND" {{cellcolors||#888}} Ground | ||

|- | |- | ||

| | | data-sort-value="0A30" | A30 || {{cellcolors|#f93|#fff}} VDD || +1.0V_BE_VDDC || {{pin}} || data-sort-value="Z1.0V" | Connected to [[Regulators#iPowIR_IP2003ATRPBF_.2840A_Synchronous_Buck_Multiphase_Optimized_LGA_Power_Block.29|iPowIR IP2003ATRPBF]] (3 units) pin 6 (Vsw) through NEC/TOKIN proadlizers | ||

|- | |- | ||

| | | data-sort-value="0A31" | A31 || {{cellcolors|#333|#fff}} GND || GND || {{pin}} || data-sort-value="ZGND" {{cellcolors||#888}} Ground | ||

|- | |- | ||

| | | data-sort-value="0A32" | A32 || {{cellcolors|#f93|#fff}} VDD || +1.0V_BE_VDDC || {{pin}} || data-sort-value="Z1.0V" | Connected to [[Regulators#iPowIR_IP2003ATRPBF_.2840A_Synchronous_Buck_Multiphase_Optimized_LGA_Power_Block.29|iPowIR IP2003ATRPBF]] (3 units) pin 6 (Vsw) through NEC/TOKIN proadlizers | ||

|- | |- | ||

| | | data-sort-value="0A33" | A33 || {{cellcolors|#333|#fff}} GND || GND || {{pin}} || data-sort-value="ZGND" {{cellcolors||#888}} Ground | ||

|- | |- | ||

| | | data-sort-value="0A34" | A34 || {{cellcolors|#333|#fff}} RC_XCLK_EN || GND || {{pin}} || data-sort-value="ZGND" {{cellcolors||#888}} Ground | ||

|- | |- | ||

| | | data-sort-value="0A35" | A35 || RC_SCAN_CLK2 || || {{pin}} || Resistor 470K ohms (R1001) to GND | ||

|- | |- | ||

| | | data-sort-value="0A36" | A36 || RC_SCAN_CLK1 || || {{pin}} || Resistor 470K ohms (R1002) to GND | ||

|- | |- | ||

| | | data-sort-value="0A37" | A37 || RC_SCAN_CLK0 || || {{pin}} || Resistor 470K ohms (R1003) to GND | ||

|- | |- | ||

| | | data-sort-value="0A38" | A38 || {{cellcolors|#333|#fff}} GND || GND || {{pin}} || data-sort-value="ZGND" {{cellcolors||#888}} Ground | ||

|- | |- | ||

| | | data-sort-value="0A39" | A39 || {{cellcolors|#d53|#fff}} RC_VDDIO || data-sort-value="+1.2V_YC_RC_VDDIO" {{cellcolors|#eee|#888}} N/C || data-sort-value="ZZ" {{pinnc}} || data-sort-value="ZZ" {{cellcolors||#888}} Not Connected | ||

|- | |- | ||

| | | data-sort-value="0A40" | A40 || {{cellcolors|#d53|#fff}} RC_VDDIO || +1.2V_YC_RC_VDDIO || {{pin}} || data-sort-value="Z1.2V_YC" | Connected to [https://www.digikey.com/en/products/detail/vishay-siliconix/SUD40N02-08-E3/2623039 Vishay Siliconix SUD40N02-08-E3] pin 3 | ||

|- | |- | ||

| | | data-sort-value="0A41" | A41 || {{cellcolors|#333|#fff}} GND || GND || {{pin}} || data-sort-value="ZGND" {{cellcolors||#888}} Ground | ||

|- | |- | ||

| | | data-sort-value="0A99" style="padding:0px" | || colspan="4" data-sort-value="ZZZZ" style="padding:0px" | | ||

|- | |- | ||

| | | data-sort-value="0B01" | B1 || {{cellcolors|#d53|#fff}} YC_VDDIO || +1.2V_YC_RC_VDDIO || {{pin}} || data-sort-value="Z1.2V_YC" | Connected to [https://www.digikey.com/en/products/detail/vishay-siliconix/SUD40N02-08-E3/2623039 Vishay Siliconix SUD40N02-08-E3] pin 3 | ||

|- | |- | ||

| | | data-sort-value="0B02" | B2 || Y0_DQ1_5 || Y0_XDR0_DQ10 || {{pino}} || Connected to [[RAM|XDR DRAM]] Y0_XDR0 (first chip) pad <abbr title="Unknown">UNK</abbr> | ||

|- | |- | ||

| | | data-sort-value="0B03" | B3 || Y0_DQ1_2 || data-sort-value="Y0_XDR0_DQ06" | Y0_XDR0_DQ6 || {{pino}} || Connected to [[RAM|XDR DRAM]] Y0_XDR0 (first chip) pad <abbr title="Unknown">UNK</abbr> | ||

|- | |- | ||

| | | data-sort-value="0B04" | B4 || Y0_DQ0_6 || Y0_XDR0_DQ14 || {{pino}} || Connected to [[RAM|XDR DRAM]] Y0_XDR0 (first chip) pad <abbr title="Unknown">UNK</abbr> | ||

|- | |- | ||

| | | data-sort-value="0B05" | B5 || Y0_DQ0_4 || data-sort-value="Y0_XDR0_DQ02" | Y0_XDR0_DQ2 || {{pino}} || Connected to [[RAM|XDR DRAM]] Y0_XDR0 (first chip) pad <abbr title="Unknown">UNK</abbr> | ||

|- | |- | ||

| | | data-sort-value="0B06" | B6 || {{cellcolors|#d53|#fff}} YC_VDDIO || +1.2V_YC_RC_VDDIO || {{pin}} || data-sort-value="Z1.2V_YC" | Connected to [https://www.digikey.com/en/products/detail/vishay-siliconix/SUD40N02-08-E3/2623039 Vishay Siliconix SUD40N02-08-E3] pin 3 | ||

|- | |- | ||

| | | data-sort-value="0B07" | B7 || data-sort-value="ZZZ" {{cellcolors|#eee|#888}} N/A || data-sort-value="ZZZ" {{cellcolors|#eee|#888}} N/A || data-sort-value="ZZZ" {{cellcolors|#eee|#888}} N/A || data-sort-value="ZZZ" {{cellcolors||#888}} Missing pad | ||

|- | |- | ||

| | | data-sort-value="0B08" | B8 || Y0_DQ0_1 || Y0_XDR1_DQ14 || {{pino}} || Connected to [[RAM|XDR DRAM]] Y0_XDR1 (second chip) pad <abbr title="Unknown">UNK</abbr> | ||

|- | |- | ||

| | | data-sort-value="0B09" | B9 || data-sort-value="ZZZ" {{cellcolors|#eee|#888}} N/A || data-sort-value="ZZZ" {{cellcolors|#eee|#888}} N/A || data-sort-value="ZZZ" {{cellcolors|#eee|#888}} N/A || data-sort-value="ZZZ" {{cellcolors||#888}} Missing pad | ||

|- | |- | ||

| | | data-sort-value="0B10" | B10 || {{cellcolors|#d53|#fff}} YC_VDDIO || +1.2V_YC_RC_VDDIO || {{pin}} || data-sort-value="Z1.2V_YC" | Connected to [https://www.digikey.com/en/products/detail/vishay-siliconix/SUD40N02-08-E3/2623039 Vishay Siliconix SUD40N02-08-E3] pin 3 | ||

|- | |- | ||

| | | data-sort-value="0B11" | B11 || {{cellcolors|#d53|#fff}} Y0_DQ0_VREF || +1.2V_YC_RC_VDDIO || {{pin}} || data-sort-value="Z1.2V_YC" | Connected to [https://www.digikey.com/en/products/detail/vishay-siliconix/SUD40N02-08-E3/2623039 Vishay Siliconix SUD40N02-08-E3] pin 3 | ||

|- | |- | ||

| | | data-sort-value="0B12" | B12 || {{cellcolors|#333|#fff}} GND || GND || {{pin}} || data-sort-value="ZGND" {{cellcolors||#888}} Ground | ||

|- | |- | ||

| | | data-sort-value="0B13" | B13 || {{cellcolors|#f93|#fff}} VDD || +1.0V_BE_VDDC || {{pin}} || data-sort-value="Z1.0V" | Connected to [[Regulators#iPowIR_IP2003ATRPBF_.2840A_Synchronous_Buck_Multiphase_Optimized_LGA_Power_Block.29|iPowIR IP2003ATRPBF]] (3 units) pin 6 (Vsw) through NEC/TOKIN proadlizers | ||

|- | |- | ||

| | | data-sort-value="0B14" | B14 || {{cellcolors|#333|#fff}} GND || GND || {{pin}} || data-sort-value="ZGND" {{cellcolors||#888}} Ground | ||

|- | |- | ||

| | | data-sort-value="0B15" | B15 || {{cellcolors|#f93|#fff}} VDD || +1.0V_BE_VDDC || {{pin}} || data-sort-value="Z1.0V" | Connected to [[Regulators#iPowIR_IP2003ATRPBF_.2840A_Synchronous_Buck_Multiphase_Optimized_LGA_Power_Block.29|iPowIR IP2003ATRPBF]] (3 units) pin 6 (Vsw) through NEC/TOKIN proadlizers | ||

|- | |- | ||

| | | data-sort-value="0B16" | B16 || {{cellcolors|#333|#fff}} GND || GND || {{pin}} || data-sort-value="ZGND" {{cellcolors||#888}} Ground | ||

|- | |- | ||

| | | data-sort-value="0B17" | B17 || {{cellcolors|#f93|#fff}} VDD || +1.0V_BE_VDDC || {{pin}} || data-sort-value="Z1.0V" | Connected to [[Regulators#iPowIR_IP2003ATRPBF_.2840A_Synchronous_Buck_Multiphase_Optimized_LGA_Power_Block.29|iPowIR IP2003ATRPBF]] (3 units) pin 6 (Vsw) through NEC/TOKIN proadlizers | ||

|- | |- | ||

| | | data-sort-value="0B18" | B18 || {{cellcolors|#333|#fff}} GND || GND || {{pin}} || data-sort-value="ZGND" {{cellcolors||#888}} Ground | ||

|- | |- | ||

| | | data-sort-value="0B19" | B19 || {{cellcolors|#f93|#fff}} VDD || +1.0V_BE_VDDC || {{pin}} || data-sort-value="Z1.0V" | Connected to [[Regulators#iPowIR_IP2003ATRPBF_.2840A_Synchronous_Buck_Multiphase_Optimized_LGA_Power_Block.29|iPowIR IP2003ATRPBF]] (3 units) pin 6 (Vsw) through NEC/TOKIN proadlizers | ||

|- | |- | ||

| | | data-sort-value="0B20" | B20 || {{cellcolors|#333|#fff}} GND || GND || {{pin}} || data-sort-value="ZGND" {{cellcolors||#888}} Ground | ||

|- | |- | ||

| | | data-sort-value="0B21" | B21 || {{cellcolors|#f93|#fff}} VDD || +1.0V_BE_VDDC || {{pin}} || data-sort-value="Z1.0V" | Connected to [[Regulators#iPowIR_IP2003ATRPBF_.2840A_Synchronous_Buck_Multiphase_Optimized_LGA_Power_Block.29|iPowIR IP2003ATRPBF]] (3 units) pin 6 (Vsw) through NEC/TOKIN proadlizers | ||

|- | |- | ||

| | | data-sort-value="0B22" | B22 || {{cellcolors|#333|#fff}} GND || GND || {{pin}} || data-sort-value="ZGND" {{cellcolors||#888}} Ground | ||

|- | |- | ||

|- | | data-sort-value="0B23" | B23 || {{cellcolors|#f93|#fff}} VDD || +1.0V_BE_VDDC || {{pin}} || data-sort-value="Z1.0V" | Connected to [[Regulators#iPowIR_IP2003ATRPBF_.2840A_Synchronous_Buck_Multiphase_Optimized_LGA_Power_Block.29|iPowIR IP2003ATRPBF]] (3 units) pin 6 (Vsw) through NEC/TOKIN proadlizers | ||

|- | |- | ||

| data-sort-value="0B24" | B24 || {{cellcolors|#333|#fff}} GND || GND || {{pin}} || data-sort-value="ZGND" {{cellcolors||#888}} Ground | |||

|- | |- | ||

| | | data-sort-value="0B25" | B25 || {{cellcolors|#f93|#fff}} VDD || +1.0V_BE_VDDC || {{pin}} || data-sort-value="Z1.0V" | Connected to [[Regulators#iPowIR_IP2003ATRPBF_.2840A_Synchronous_Buck_Multiphase_Optimized_LGA_Power_Block.29|iPowIR IP2003ATRPBF]] (3 units) pin 6 (Vsw) through NEC/TOKIN proadlizers | ||

|- | |- | ||

| | | data-sort-value="0B26" | B26 || {{cellcolors|#333|#fff}} GND || GND || {{pin}} || data-sort-value="ZGND" {{cellcolors||#888}} Ground | ||

|- | |- | ||

| | | data-sort-value="0B27" | B27 || {{cellcolors|#f93|#fff}} VDD || +1.0V_BE_VDDC || {{pin}} || data-sort-value="Z1.0V" | Connected to [[Regulators#iPowIR_IP2003ATRPBF_.2840A_Synchronous_Buck_Multiphase_Optimized_LGA_Power_Block.29|iPowIR IP2003ATRPBF]] (3 units) pin 6 (Vsw) through NEC/TOKIN proadlizers | ||

|- | |- | ||

| | | data-sort-value="0B28" | B28 || {{cellcolors|#333|#fff}} GND || GND || {{pin}} || data-sort-value="ZGND" {{cellcolors||#888}} Ground | ||

|- | |- | ||

| | | data-sort-value="0B29" | B29 || {{cellcolors|#f93|#fff}} VDD || +1.0V_BE_VDDC || {{pin}} || data-sort-value="Z1.0V" | Connected to [[Regulators#iPowIR_IP2003ATRPBF_.2840A_Synchronous_Buck_Multiphase_Optimized_LGA_Power_Block.29|iPowIR IP2003ATRPBF]] (3 units) pin 6 (Vsw) through NEC/TOKIN proadlizers | ||

|- | |- | ||

| | | data-sort-value="0B30" | B30 || {{cellcolors|#333|#fff}} GND || GND || {{pin}} || data-sort-value="ZGND" {{cellcolors||#888}} Ground | ||

|- | |- | ||

| | | data-sort-value="0B31" | B31 || {{cellcolors|#f93|#fff}} VDD || +1.0V_BE_VDDC || {{pin}} || data-sort-value="Z1.0V" | Connected to [[Regulators#iPowIR_IP2003ATRPBF_.2840A_Synchronous_Buck_Multiphase_Optimized_LGA_Power_Block.29|iPowIR IP2003ATRPBF]] (3 units) pin 6 (Vsw) through NEC/TOKIN proadlizers | ||

|- | |- | ||

| | | data-sort-value="0B32" | B32 || {{cellcolors|#333|#fff}} GND || GND || {{pin}} || data-sort-value="ZGND" {{cellcolors||#888}} Ground | ||

|- | |- | ||

| | | data-sort-value="0B33" | B33 || {{cellcolors|#f93|#fff}} VDD || +1.0V_BE_VDDC || {{pin}} || data-sort-value="Z1.0V" | Connected to [[Regulators#iPowIR_IP2003ATRPBF_.2840A_Synchronous_Buck_Multiphase_Optimized_LGA_Power_Block.29|iPowIR IP2003ATRPBF]] (3 units) pin 6 (Vsw) through NEC/TOKIN proadlizers | ||

|- | |- | ||

| | | data-sort-value="0B34" | B34 || RC_SCAN_CLK3 || || {{pin}} || Resistor 470K ohms (R1004) to GND | ||

|- | |- | ||

| | | data-sort-value="0B35" | B35 || TX0_TXN1 || BE_TX0_TXN1 || {{pino}} || Connected to [[RSX]] pad <abbr title="Unknown">UNK</abbr> ([[Template:RSX pad layout 41x41|41x41 layout]]) | ||

|- | |- | ||

| | | data-sort-value="0B36" | B36 || TX0_TXP1 || BE_TX0_TXP1 || {{pino}} || Connected to [[RSX]] pad <abbr title="Unknown">UNK</abbr> ([[Template:RSX pad layout 41x41|41x41 layout]]) | ||

|- | |- | ||

| | | data-sort-value="0B37" | B37 || {{cellcolors|#333|#fff}} GND || GND || {{pin}} || data-sort-value="ZGND" {{cellcolors||#888}} Ground | ||

|- | |- | ||

| | | data-sort-value="0B38" | B38 || TX0_TXN2 || BE_TX0_TXN2 || {{pino}} || Connected to [[RSX]] pad <abbr title="Unknown">UNK</abbr> ([[Template:RSX pad layout 41x41|41x41 layout]]) | ||

|- | |- | ||

| | | data-sort-value="0B39" | B39 || TX0_TXP2 || BE_TX0_TXP2 || {{pino}} || Connected to [[RSX]] pad <abbr title="Unknown">UNK</abbr> ([[Template:RSX pad layout 41x41|41x41 layout]]) | ||

|- | |- | ||

| | | data-sort-value="0B40" | B40 || TX0_TXN0 || BE_TX0_TXN0 || {{pino}} || Connected to [[RSX]] pad <abbr title="Unknown">UNK</abbr> ([[Template:RSX pad layout 41x41|41x41 layout]]) | ||

|- | |- | ||

| | | data-sort-value="0B41" | B41 || TX0_TXP0 || BE_TX0_TXP0 || {{pino}} || Connected to [[RSX]] pad <abbr title="Unknown">UNK</abbr> ([[Template:RSX pad layout 41x41|41x41 layout]]) | ||

|- | |- | ||

| | | data-sort-value="0B99" style="padding:0px" | || colspan="4" data-sort-value="ZZZZ" style="padding:0px" | | ||

|- | |- | ||

| | | data-sort-value="0C01" | C1 || {{cellcolors|#333|#fff}} GND || GND || {{pin}} || data-sort-value="ZGND" {{cellcolors||#888}} Ground | ||

|- | |- | ||

| | | data-sort-value="0C02" | C2 || Y0_DQ1N_6 || data-sort-value="Y0_XDR0_DQN00" | Y0_XDR0_DQN0 || {{pino}} || Connected to [[RAM|XDR DRAM]] Y0_XDR0 (first chip) pad <abbr title="Unknown">UNK</abbr> | ||

|- | |- | ||

| | | data-sort-value="0C03" | C3 || Y0_DQ1N_4 || Y0_XDR0_DQN12 || {{pino}} || Connected to [[RAM|XDR DRAM]] Y0_XDR0 (first chip) pad <abbr title="Unknown">UNK</abbr> | ||

|- | |- | ||

| | | data-sort-value="0C04" | C4 || Y0_DQ0N_0 || data-sort-value="Y0_XDR0_DQN04" | Y0_XDR0_DQN4 || {{pino}} || Connected to [[RAM|XDR DRAM]] Y0_XDR0 (first chip) pad <abbr title="Unknown">UNK</abbr> | ||

|- | |- | ||

| | | data-sort-value="0C05" | C5 || Y0_DQ0N_5 || data-sort-value="Y0_XDR0_DQN08" | Y0_XDR0_DQN8 || {{pino}} || Connected to [[RAM|XDR DRAM]] Y0_XDR0 (first chip) pad <abbr title="Unknown">UNK</abbr> | ||

|- | |- | ||

| | | data-sort-value="0C06" | C6 || Y0_DQ1N_8 || data-sort-value="ZZ" {{cellcolors|#eee|#888}} N/C || data-sort-value="ZZ" {{pinnc}} || data-sort-value="ZZ" {{cellcolors||#888}} Not Connected | ||

|- | |- | ||

| | | data-sort-value="0C07" | C7 || Y0_DQ1N_3 || Y0_XDR1_DQN10 || {{pino}} || Connected to [[RAM|XDR DRAM]] Y0_XDR1 (second chip) pad <abbr title="Unknown">UNK</abbr> | ||

|- | |- | ||

| | | data-sort-value="0C08" | C8 || Y0_DQ1N_1 || data-sort-value="Y0_XDR1_DQN06" | Y0_XDR1_DQN6 || {{pino}} || Connected to [[RAM|XDR DRAM]] Y0_XDR1 (second chip) pad <abbr title="Unknown">UNK</abbr> | ||

|- | |- | ||

| | | data-sort-value="0C09" | C9 || Y0_DQ0N_3 || data-sort-value="Y0_XDR1_DQN02" | Y0_XDR1_DQN2 || {{pino}} || Connected to [[RAM|XDR DRAM]] Y0_XDR1 (second chip) pad <abbr title="Unknown">UNK</abbr> | ||

|- | |- | ||

| | | data-sort-value="0C10" | C10 || Y0_DQ0N_8 || data-sort-value="ZZ" {{cellcolors|#eee|#888}} N/C || data-sort-value="ZZ" {{pinnc}} || data-sort-value="ZZ" {{cellcolors||#888}} Not Connected | ||

|- | |- | ||

| | | data-sort-value="0C11" | C11 || {{cellcolors|#930|#fff}} VDDS1 || BE_VDDS1 || {{pino}} || data-sort-value="Z1.6V" | Connected to [[Regulators#OnSemi_NCP5318FTR2G_.28Two.2FThree.2FFour-Phase_Buck_CPU_Controller.29| Onsemi NCP5318FTR2G]] pin 5 (VFFB) and 11 (VFB) | ||

|- | |- | ||

| | | data-sort-value="0C12" | C12 || {{cellcolors|#f93|#fff}} VDD || +1.0V_BE_VDDC || {{pin}} || data-sort-value="Z1.0V" | Connected to [[Regulators#iPowIR_IP2003ATRPBF_.2840A_Synchronous_Buck_Multiphase_Optimized_LGA_Power_Block.29|iPowIR IP2003ATRPBF]] (3 units) pin 6 (Vsw) through NEC/TOKIN proadlizers | ||

|- | |- | ||

| | | data-sort-value="0C13" | C13 || {{cellcolors|#333|#fff}} GND || GND || {{pin}} || data-sort-value="ZGND" {{cellcolors||#888}} Ground | ||

|- | |- | ||

| | | data-sort-value="0C14" | C14 || {{cellcolors|#f93|#fff}} VDD || +1.0V_BE_VDDC || {{pin}} || data-sort-value="Z1.0V" | Connected to [[Regulators#iPowIR_IP2003ATRPBF_.2840A_Synchronous_Buck_Multiphase_Optimized_LGA_Power_Block.29|iPowIR IP2003ATRPBF]] (3 units) pin 6 (Vsw) through NEC/TOKIN proadlizers | ||

|- | |- | ||

| | | data-sort-value="0C15" | C15 || {{cellcolors|#333|#fff}} GND || GND || {{pin}} || data-sort-value="ZGND" {{cellcolors||#888}} Ground | ||

|- | |- | ||

| | | data-sort-value="0C16" | C16 || {{cellcolors|#f93|#fff}} VDD || +1.0V_BE_VDDC || {{pin}} || data-sort-value="Z1.0V" | Connected to [[Regulators#iPowIR_IP2003ATRPBF_.2840A_Synchronous_Buck_Multiphase_Optimized_LGA_Power_Block.29|iPowIR IP2003ATRPBF]] (3 units) pin 6 (Vsw) through NEC/TOKIN proadlizers | ||

|- | |- | ||

| | | data-sort-value="0C17" | C17 || {{cellcolors|#333|#fff}} GND || GND || {{pin}} || data-sort-value="ZGND" {{cellcolors||#888}} Ground | ||

|- | |- | ||

| | | data-sort-value="0C18" | C18 || {{cellcolors|#f93|#fff}} VDD || +1.0V_BE_VDDC || {{pin}} || data-sort-value="Z1.0V" | Connected to [[Regulators#iPowIR_IP2003ATRPBF_.2840A_Synchronous_Buck_Multiphase_Optimized_LGA_Power_Block.29|iPowIR IP2003ATRPBF]] (3 units) pin 6 (Vsw) through NEC/TOKIN proadlizers | ||

|- | |- | ||

| | | data-sort-value="0C19" | C19 || {{cellcolors|#333|#fff}} GND || GND || {{pin}} || data-sort-value="ZGND" {{cellcolors||#888}} Ground | ||

|- | |- | ||

| | | data-sort-value="0C20" | C20 || {{cellcolors|#f93|#fff}} VDD || +1.0V_BE_VDDC || {{pin}} || data-sort-value="Z1.0V" | Connected to [[Regulators#iPowIR_IP2003ATRPBF_.2840A_Synchronous_Buck_Multiphase_Optimized_LGA_Power_Block.29|iPowIR IP2003ATRPBF]] (3 units) pin 6 (Vsw) through NEC/TOKIN proadlizers | ||

|- | |- | ||

| | | data-sort-value="0C21" | C21 || {{cellcolors|#333|#fff}} GND || GND || {{pin}} || data-sort-value="ZGND" {{cellcolors||#888}} Ground | ||

|- | |- | ||

|- | | data-sort-value="0C22" | C22 || {{cellcolors|#f93|#fff}} VDD || +1.0V_BE_VDDC || {{pin}} || data-sort-value="Z1.0V" | Connected to [[Regulators#iPowIR_IP2003ATRPBF_.2840A_Synchronous_Buck_Multiphase_Optimized_LGA_Power_Block.29|iPowIR IP2003ATRPBF]] (3 units) pin 6 (Vsw) through NEC/TOKIN proadlizers | ||

|- | |- | ||

| data-sort-value="0C23" | C23 || {{cellcolors|#333|#fff}} GND || GND || {{pin}} || data-sort-value="ZGND" {{cellcolors||#888}} Ground | |||

|- | |- | ||

| | | data-sort-value="0C24" | C24 || {{cellcolors|#f93|#fff}} VDD || +1.0V_BE_VDDC || {{pin}} || data-sort-value="Z1.0V" | Connected to [[Regulators#iPowIR_IP2003ATRPBF_.2840A_Synchronous_Buck_Multiphase_Optimized_LGA_Power_Block.29|iPowIR IP2003ATRPBF]] (3 units) pin 6 (Vsw) through NEC/TOKIN proadlizers | ||

|- | |- | ||

| | | data-sort-value="0C25" | C25 || {{cellcolors|#333|#fff}} GND || GND || {{pin}} || data-sort-value="ZGND" {{cellcolors||#888}} Ground | ||

|- | |- | ||

| | | data-sort-value="0C26" | C26 || {{cellcolors|#f93|#fff}} VDD || +1.0V_BE_VDDC || {{pin}} || data-sort-value="Z1.0V" | Connected to [[Regulators#iPowIR_IP2003ATRPBF_.2840A_Synchronous_Buck_Multiphase_Optimized_LGA_Power_Block.29|iPowIR IP2003ATRPBF]] (3 units) pin 6 (Vsw) through NEC/TOKIN proadlizers | ||

|- | |- | ||

| | | data-sort-value="0C27" | C27 || {{cellcolors|#333|#fff}} GND || GND || {{pin}} || data-sort-value="ZGND" {{cellcolors||#888}} Ground | ||

|- | |- | ||

| | | data-sort-value="0C28" | C28 || {{cellcolors|#f93|#fff}} VDD || +1.0V_BE_VDDC || {{pin}} || data-sort-value="Z1.0V" | Connected to [[Regulators#iPowIR_IP2003ATRPBF_.2840A_Synchronous_Buck_Multiphase_Optimized_LGA_Power_Block.29|iPowIR IP2003ATRPBF]] (3 units) pin 6 (Vsw) through NEC/TOKIN proadlizers | ||

|- | |- | ||

| | | data-sort-value="0C29" | C29 || {{cellcolors|#333|#fff}} GND || GND || {{pin}} || data-sort-value="ZGND" {{cellcolors||#888}} Ground | ||

|- | |- | ||

| | | data-sort-value="0C30" | C30 || {{cellcolors|#f93|#fff}} VDD || +1.0V_BE_VDDC || {{pin}} || data-sort-value="Z1.0V" | Connected to [[Regulators#iPowIR_IP2003ATRPBF_.2840A_Synchronous_Buck_Multiphase_Optimized_LGA_Power_Block.29|iPowIR IP2003ATRPBF]] (3 units) pin 6 (Vsw) through NEC/TOKIN proadlizers | ||

|- | |- | ||

| | | data-sort-value="0C31" | C31 || {{cellcolors|#333|#fff}} GND || GND || {{pin}} || data-sort-value="ZGND" {{cellcolors||#888}} Ground | ||

|- | |- | ||

| | | data-sort-value="0C32" | C32 || {{cellcolors|#f93|#fff}} VDD || +1.0V_BE_VDDC || {{pin}} || data-sort-value="Z1.0V" | Connected to [[Regulators#iPowIR_IP2003ATRPBF_.2840A_Synchronous_Buck_Multiphase_Optimized_LGA_Power_Block.29|iPowIR IP2003ATRPBF]] (3 units) pin 6 (Vsw) through NEC/TOKIN proadlizers | ||

|- | |- | ||

| | | data-sort-value="0C33" | C33 || {{cellcolors|#333|#fff}} GND || GND || {{pin}} || data-sort-value="ZGND" {{cellcolors||#888}} Ground | ||

|- | |- | ||

| | | data-sort-value="0C34" | C34 || {{cellcolors|#333|#fff}} GND || GND || {{pin}} || data-sort-value="ZGND" {{cellcolors||#888}} Ground | ||

|- | |- | ||

| | | data-sort-value="0C35" | C35 || TX0_TXN3 || BE_TX0_TXN3 || {{pino}} || Connected to [[RSX]] pad <abbr title="Unknown">UNK</abbr> ([[Template:RSX pad layout 41x41|41x41 layout]]) | ||

|- | |- | ||

| | | data-sort-value="0C36" | C36 || TX0_TXP3 || BE_TX0_TXP3 || {{pino}} || Connected to [[RSX]] pad <abbr title="Unknown">UNK</abbr> ([[Template:RSX pad layout 41x41|41x41 layout]]) | ||

|- | |- | ||

| | | data-sort-value="0C37" | C37 || {{cellcolors|#333|#fff}} GND || GND || {{pin}} || data-sort-value="ZGND" {{cellcolors||#888}} Ground | ||

|- | |- | ||

| | | data-sort-value="0C38" | C38 || TX0_TXCLKN || BE_TX0_TXCLKN || {{pino}} || Connected to [[RSX]] pad <abbr title="Unknown">UNK</abbr> ([[Template:RSX pad layout 41x41|41x41 layout]]) | ||

|- | |- | ||

| | | data-sort-value="0C39" | C39 || TX0_TXCLKP || BE_TX0_TXCLKP || {{pino}} || Connected to [[RSX]] pad <abbr title="Unknown">UNK</abbr> ([[Template:RSX pad layout 41x41|41x41 layout]]) | ||

|- | |- | ||

| | | data-sort-value="0C40" | C40 || data-sort-value="ZZZ" {{cellcolors|#eee|#888}} N/A || data-sort-value="ZZZ" {{cellcolors|#eee|#888}} N/A || data-sort-value="ZZZ" {{cellcolors|#eee|#888}} N/A || data-sort-value="ZZZ" {{cellcolors||#888}} Missing pad | ||

|- | |- | ||

| | | data-sort-value="0C41" | C41 || data-sort-value="ZZZ" {{cellcolors|#eee|#888}} N/A || data-sort-value="ZZZ" {{cellcolors|#eee|#888}} N/A || data-sort-value="ZZZ" {{cellcolors|#eee|#888}} N/A || data-sort-value="ZZZ" {{cellcolors||#888}} Missing pad | ||

|- | |- | ||

| | | data-sort-value="0C99" style="padding:0px" | || colspan="4" data-sort-value="ZZZZ" style="padding:0px" | | ||

|- | |- | ||

| | | data-sort-value="0D01" | D1 || {{cellcolors|#333|#fff}} GND || GND || {{pin}} || data-sort-value="ZGND" {{cellcolors||#888}} Ground | ||

|- | |- | ||

| | | data-sort-value="0D02" | D2 || Y0_DQ1_6 || data-sort-value="Y0_XDR0_DQ00" | Y0_XDR0_DQ0 || {{pino}} || Connected to [[RAM|XDR DRAM]] Y0_XDR0 (first chip) pad <abbr title="Unknown">UNK</abbr> | ||

|- | |- | ||

| | | data-sort-value="0D03" | D3 || Y0_DQ1_4 || Y0_XDR0_DQ12 || {{pino}} || Connected to [[RAM|XDR DRAM]] Y0_XDR0 (first chip) pad <abbr title="Unknown">UNK</abbr> | ||

|- | |- | ||

| | | data-sort-value="0D04" | D4 || Y0_DQ0_0 || data-sort-value="Y0_XDR0_DQ04" | Y0_XDR0_DQ4 || {{pino}} || Connected to [[RAM|XDR DRAM]] Y0_XDR0 (first chip) pad <abbr title="Unknown">UNK</abbr> | ||

|- | |- | ||

| | | data-sort-value="0D05" | D5 || Y0_DQ0_5 || data-sort-value="Y0_XDR0_DQ08" | Y0_XDR0_DQ8 || {{pino}} || Connected to [[RAM|XDR DRAM]] Y0_XDR0 (first chip) pad <abbr title="Unknown">UNK</abbr> | ||

|- | |- | ||

| | | data-sort-value="0D06" | D6 || Y0_DQ1_8 || data-sort-value="ZZ" {{cellcolors|#eee|#888}} N/C || data-sort-value="ZZ" {{pinnc}} || data-sort-value="ZZ" {{cellcolors||#888}} Not Connected | ||

|- | |- | ||

| | | data-sort-value="0D07" | D7 || Y0_DQ1_3 || Y0_XDR1_DQ10 || {{pino}} || Connected to [[RAM|XDR DRAM]] Y0_XDR1 (second chip) pad <abbr title="Unknown">UNK</abbr> | ||

|- | |- | ||

| | | data-sort-value="0D08" | D8 || Y0_DQ1_1 || data-sort-value="Y0_XDR1_DQ06" | Y0_XDR1_DQ6 || {{pino}} || Connected to [[RAM|XDR DRAM]] Y0_XDR1 (second chip) pad <abbr title="Unknown">UNK</abbr> | ||

|- | |- | ||

| | | data-sort-value="0D09" | D9 || Y0_DQ0_3 || data-sort-value="Y0_XDR1_DQ02" | Y0_XDR1_DQ2 || {{pino}} || Connected to [[RAM|XDR DRAM]] Y0_XDR1 (second chip) pad <abbr title="Unknown">UNK</abbr> | ||

|- | |- | ||

| | | data-sort-value="0D10" | D10 || Y0_DQ0_8 || data-sort-value="ZZ" {{cellcolors|#eee|#888}} N/C || data-sort-value="ZZ" {{pinnc}} || data-sort-value="ZZ" {{cellcolors||#888}} Not Connected | ||

|- | |- | ||

| | | data-sort-value="0D11" | D11 || {{cellcolors|#930|#fff}} VDDS2 || BE_VDDS2 || {{pino}} || data-sort-value="Z1.6V" | Connected to [[Regulators#OnSemi_NCP5318FTR2G_.28Two.2FThree.2FFour-Phase_Buck_CPU_Controller.29| Onsemi NCP5318FTR2G]] pin 9 (SGND) | ||

|- | |- | ||

| | | data-sort-value="0D12" | D12 || {{cellcolors|#333|#fff}} GND || GND || {{pin}} || data-sort-value="ZGND" {{cellcolors||#888}} Ground | ||

|- | |- | ||

| | | data-sort-value="0D13" | D13 || {{cellcolors|#f93|#fff}} VDD || +1.0V_BE_VDDC || {{pin}} || data-sort-value="Z1.0V" | Connected to [[Regulators#iPowIR_IP2003ATRPBF_.2840A_Synchronous_Buck_Multiphase_Optimized_LGA_Power_Block.29|iPowIR IP2003ATRPBF]] (3 units) pin 6 (Vsw) through NEC/TOKIN proadlizers | ||

|- | |- | ||

| | | data-sort-value="0D14" | D14 || {{cellcolors|#333|#fff}} GND || GND || {{pin}} || data-sort-value="ZGND" {{cellcolors||#888}} Ground | ||

|- | |- | ||

| | | data-sort-value="0D15" | D15 || {{cellcolors|#f93|#fff}} VDD || +1.0V_BE_VDDC || {{pin}} || data-sort-value="Z1.0V" | Connected to [[Regulators#iPowIR_IP2003ATRPBF_.2840A_Synchronous_Buck_Multiphase_Optimized_LGA_Power_Block.29|iPowIR IP2003ATRPBF]] (3 units) pin 6 (Vsw) through NEC/TOKIN proadlizers | ||

|- | |- | ||

| | | data-sort-value="0D16" | D16 || {{cellcolors|#333|#fff}} GND || GND || {{pin}} || data-sort-value="ZGND" {{cellcolors||#888}} Ground | ||

|- | |- | ||

| | | data-sort-value="0D17" | D17 || {{cellcolors|#f93|#fff}} VDD || +1.0V_BE_VDDC || {{pin}} || data-sort-value="Z1.0V" | Connected to [[Regulators#iPowIR_IP2003ATRPBF_.2840A_Synchronous_Buck_Multiphase_Optimized_LGA_Power_Block.29|iPowIR IP2003ATRPBF]] (3 units) pin 6 (Vsw) through NEC/TOKIN proadlizers | ||

|- | |- | ||

| | | data-sort-value="0D18" | D18 || {{cellcolors|#333|#fff}} GND || GND || {{pin}} || data-sort-value="ZGND" {{cellcolors||#888}} Ground | ||

|- | |- | ||

| | | data-sort-value="0D19" | D19 || {{cellcolors|#f93|#fff}} VDD || +1.0V_BE_VDDC || {{pin}} || data-sort-value="Z1.0V" | Connected to [[Regulators#iPowIR_IP2003ATRPBF_.2840A_Synchronous_Buck_Multiphase_Optimized_LGA_Power_Block.29|iPowIR IP2003ATRPBF]] (3 units) pin 6 (Vsw) through NEC/TOKIN proadlizers | ||

|- | |- | ||

| | | data-sort-value="0D20" | D20 || {{cellcolors|#333|#fff}} GND || GND || {{pin}} || data-sort-value="ZGND" {{cellcolors||#888}} Ground | ||

|- | |- | ||

|- | | data-sort-value="0D21" | D21 || {{cellcolors|#f93|#fff}} VDD || +1.0V_BE_VDDC || {{pin}} || data-sort-value="Z1.0V" | Connected to [[Regulators#iPowIR_IP2003ATRPBF_.2840A_Synchronous_Buck_Multiphase_Optimized_LGA_Power_Block.29|iPowIR IP2003ATRPBF]] (3 units) pin 6 (Vsw) through NEC/TOKIN proadlizers | ||

|- | |- | ||

| data-sort-value="0D22" | D22 || {{cellcolors|#333|#fff}} GND || GND || {{pin}} || data-sort-value="ZGND" {{cellcolors||#888}} Ground | |||

|- | |- | ||

| | | data-sort-value="0D23" | D23 || {{cellcolors|#f93|#fff}} VDD || +1.0V_BE_VDDC || {{pin}} || data-sort-value="Z1.0V" | Connected to [[Regulators#iPowIR_IP2003ATRPBF_.2840A_Synchronous_Buck_Multiphase_Optimized_LGA_Power_Block.29|iPowIR IP2003ATRPBF]] (3 units) pin 6 (Vsw) through NEC/TOKIN proadlizers | ||

|- | |- | ||

| | | data-sort-value="0D24" | D24 || {{cellcolors|#333|#fff}} GND || GND || {{pin}} || data-sort-value="ZGND" {{cellcolors||#888}} Ground | ||

|- | |- | ||

| | | data-sort-value="0D25" | D25 || {{cellcolors|#f93|#fff}} VDD || +1.0V_BE_VDDC || {{pin}} || data-sort-value="Z1.0V" | Connected to [[Regulators#iPowIR_IP2003ATRPBF_.2840A_Synchronous_Buck_Multiphase_Optimized_LGA_Power_Block.29|iPowIR IP2003ATRPBF]] (3 units) pin 6 (Vsw) through NEC/TOKIN proadlizers | ||

|- | |- | ||

| | | data-sort-value="0D26" | D26 || {{cellcolors|#333|#fff}} GND || GND || {{pin}} || data-sort-value="ZGND" {{cellcolors||#888}} Ground | ||

|- | |- | ||

| | | data-sort-value="0D27" | D27 || {{cellcolors|#f93|#fff}} VDD || +1.0V_BE_VDDC || {{pin}} || data-sort-value="Z1.0V" | Connected to [[Regulators#iPowIR_IP2003ATRPBF_.2840A_Synchronous_Buck_Multiphase_Optimized_LGA_Power_Block.29|iPowIR IP2003ATRPBF]] (3 units) pin 6 (Vsw) through NEC/TOKIN proadlizers | ||

|- | |- | ||

| | | data-sort-value="0D28" | D28 || {{cellcolors|#333|#fff}} GND || GND || {{pin}} || data-sort-value="ZGND" {{cellcolors||#888}} Ground | ||

|- | |- | ||

| | | data-sort-value="0D29" | D29 || {{cellcolors|#f93|#fff}} VDD || +1.0V_BE_VDDC || {{pin}} || data-sort-value="Z1.0V" | Connected to [[Regulators#iPowIR_IP2003ATRPBF_.2840A_Synchronous_Buck_Multiphase_Optimized_LGA_Power_Block.29|iPowIR IP2003ATRPBF]] (3 units) pin 6 (Vsw) through NEC/TOKIN proadlizers | ||

|- | |- | ||

| | | data-sort-value="0D30" | D30 || {{cellcolors|#333|#fff}} GND || GND || {{pin}} || data-sort-value="ZGND" {{cellcolors||#888}} Ground | ||

|- | |- | ||

| | | data-sort-value="0D31" | D31 || {{cellcolors|#f93|#fff}} VDD || +1.0V_BE_VDDC || {{pin}} || data-sort-value="Z1.0V" | Connected to [[Regulators#iPowIR_IP2003ATRPBF_.2840A_Synchronous_Buck_Multiphase_Optimized_LGA_Power_Block.29|iPowIR IP2003ATRPBF]] (3 units) pin 6 (Vsw) through NEC/TOKIN proadlizers | ||

|- | |- | ||

| | | data-sort-value="0D32" | D32 || {{cellcolors|#333|#fff}} GND || GND || {{pin}} || data-sort-value="ZGND" {{cellcolors||#888}} Ground | ||

|- | |- | ||

| | | data-sort-value="0D33" | D33 || {{cellcolors|#f93|#fff}} VDD || +1.0V_BE_VDDC || {{pin}} || data-sort-value="Z1.0V" | Connected to [[Regulators#iPowIR_IP2003ATRPBF_.2840A_Synchronous_Buck_Multiphase_Optimized_LGA_Power_Block.29|iPowIR IP2003ATRPBF]] (3 units) pin 6 (Vsw) through NEC/TOKIN proadlizers | ||

|- | |- | ||

| | | data-sort-value="0D34" | D34 || {{cellcolors|#333|#fff}} TX0_GNDA || GND || {{pin}} || data-sort-value="ZGND" {{cellcolors||#888}} Ground | ||

|- | |- | ||

| | | data-sort-value="0D35" | D35 || TX0_TXN5 || BE_TX0_TXN5 || {{pino}} || Connected to [[RSX]] pad <abbr title="Unknown">UNK</abbr> ([[Template:RSX pad layout 41x41|41x41 layout]]) | ||

|- | |- | ||

| | | data-sort-value="0D36" | D36 || TX0_TXP5 || BE_TX0_TXP5 || {{pino}} || Connected to [[RSX]] pad <abbr title="Unknown">UNK</abbr> ([[Template:RSX pad layout 41x41|41x41 layout]]) | ||

|- | |- | ||

| | | data-sort-value="0D37" | D37 || {{cellcolors|#d53|#fff}} RC_VDDIO || +1.2V_YC_RC_VDDIO || {{pin}} || data-sort-value="Z1.2V_YC" | Connected to [https://www.digikey.com/en/products/detail/vishay-siliconix/SUD40N02-08-E3/2623039 Vishay Siliconix SUD40N02-08-E3] pin 3 | ||

|- | |- | ||

| | | data-sort-value="0D38" | D38 || TX0_TXN6 || BE_TX0_TXN6 || {{pino}} || Connected to [[RSX]] pad <abbr title="Unknown">UNK</abbr> ([[Template:RSX pad layout 41x41|41x41 layout]]) | ||

|- | |- | ||

| | | data-sort-value="0D39" | D39 || TX0_TXP6 || BE_TX0_TXP6 || {{pino}} || Connected to [[RSX]] pad <abbr title="Unknown">UNK</abbr> ([[Template:RSX pad layout 41x41|41x41 layout]]) | ||

|- | |- | ||

| | | data-sort-value="0D40" | D40 || TX0_TXN4 || BE_TX0_TXN4 || {{pino}} || Connected to [[RSX]] pad <abbr title="Unknown">UNK</abbr> ([[Template:RSX pad layout 41x41|41x41 layout]]) | ||

|- | |- | ||

| | | data-sort-value="0D41" | D41 || TX0_TXP4 || BE_TX0_TXP4 || {{pino}} || Connected to [[RSX]] pad <abbr title="Unknown">UNK</abbr> ([[Template:RSX pad layout 41x41|41x41 layout]]) | ||

|- | |- | ||

| | | data-sort-value="0D99" style="padding:0px" | || colspan="4" data-sort-value="ZZZZ" style="padding:0px" | | ||

|- | |- | ||

| | | data-sort-value="0E01" | E1 || Y0_RQ_RST || BE_Y0_RQ_RST || {{pino}} || Connected to [[RAM|XDR DRAM]] Y0_XDR0 (first chip), and Y0_XDR1 (second chip) pad C15. Serial reset | ||

|- | |- | ||

| | | data-sort-value="0E02" | E2 || {{cellcolors|#333|#fff}} GND || GND || {{pin}} || data-sort-value="ZGND" {{cellcolors||#888}} Ground | ||

|- | |- | ||

| | | data-sort-value="0E03" | E3 || {{cellcolors|#d53|#fff}} YC_VDDIO || +1.2V_YC_RC_VDDIO || {{pin}} || data-sort-value="Z1.2V_YC" | Connected to [https://www.digikey.com/en/products/detail/vishay-siliconix/SUD40N02-08-E3/2623039 Vishay Siliconix SUD40N02-08-E3] pin 3 | ||

|- | |- | ||

| | | data-sort-value="0E04" | E4 || {{cellcolors|#333|#fff}} GND || GND || {{pin}} || data-sort-value="ZGND" {{cellcolors||#888}} Ground | ||

|- | |- | ||

| | | data-sort-value="0E05" | E5 || {{cellcolors|#d53|#fff}} YC_VDDIO || +1.2V_YC_RC_VDDIO || {{pin}} || data-sort-value="Z1.2V_YC" | Connected to [https://www.digikey.com/en/products/detail/vishay-siliconix/SUD40N02-08-E3/2623039 Vishay Siliconix SUD40N02-08-E3] pin 3 | ||

|- | |- | ||

| | | data-sort-value="0E06" | E6 || {{cellcolors|#333|#fff}} GND || GND || {{pin}} || data-sort-value="ZGND" {{cellcolors||#888}} Ground | ||

|- | |- | ||

| | | data-sort-value="0E07" | E7 || {{cellcolors|#d53|#fff}} YC_VDDIO || +1.2V_YC_RC_VDDIO || {{pin}} || data-sort-value="Z1.2V_YC" | Connected to [https://www.digikey.com/en/products/detail/vishay-siliconix/SUD40N02-08-E3/2623039 Vishay Siliconix SUD40N02-08-E3] pin 3 | ||

|- | |- | ||

| | | data-sort-value="0E08" | E8 || {{cellcolors|#d53|#fff}} YC_VDDIO || +1.2V_YC_RC_VDDIO || {{pin}} || data-sort-value="Z1.2V_YC" | Connected to [https://www.digikey.com/en/products/detail/vishay-siliconix/SUD40N02-08-E3/2623039 Vishay Siliconix SUD40N02-08-E3] pin 3 | ||

|- | |- | ||

| | | data-sort-value="0E09" | E9 || {{cellcolors|#333|#fff}} GND || GND || {{pin}} || data-sort-value="ZGND" {{cellcolors||#888}} Ground | ||

|- | |- | ||

| | | data-sort-value="0E10" | E10 || {{cellcolors|#333|#fff}} GND || GND || {{pin}} || data-sort-value="ZGND" {{cellcolors||#888}} Ground | ||

|- | |- | ||

| | | data-sort-value="0E11" | E11 || {{cellcolors|#333|#fff}} VDDE || GND || {{pin}} || data-sort-value="ZGND" {{cellcolors||#888}} Ground | ||

|- | |- | ||

| | | data-sort-value="0E12" | E12 || {{cellcolors|#f93|#fff}} VDD || +1.0V_BE_VDDC || {{pin}} || data-sort-value="Z1.0V" | Connected to [[Regulators#iPowIR_IP2003ATRPBF_.2840A_Synchronous_Buck_Multiphase_Optimized_LGA_Power_Block.29|iPowIR IP2003ATRPBF]] (3 units) pin 6 (Vsw) through NEC/TOKIN proadlizers | ||

|- | |- | ||

| | | data-sort-value="0E13" | E13 || {{cellcolors|#333|#fff}} GND || GND || {{pin}} || data-sort-value="ZGND" {{cellcolors||#888}} Ground | ||

|- | |- | ||

| | | data-sort-value="0E14" | E14 || {{cellcolors|#f93|#fff}} VDD || +1.0V_BE_VDDC || {{pin}} || data-sort-value="Z1.0V" | Connected to [[Regulators#iPowIR_IP2003ATRPBF_.2840A_Synchronous_Buck_Multiphase_Optimized_LGA_Power_Block.29|iPowIR IP2003ATRPBF]] (3 units) pin 6 (Vsw) through NEC/TOKIN proadlizers | ||

|- | |- | ||

| | | data-sort-value="0E15" | E15 || {{cellcolors|#333|#fff}} GND || GND || {{pin}} || data-sort-value="ZGND" {{cellcolors||#888}} Ground | ||

|- | |- | ||

| | | data-sort-value="0E16" | E16 || {{cellcolors|#f93|#fff}} VDD || +1.0V_BE_VDDC || {{pin}} || data-sort-value="Z1.0V" | Connected to [[Regulators#iPowIR_IP2003ATRPBF_.2840A_Synchronous_Buck_Multiphase_Optimized_LGA_Power_Block.29|iPowIR IP2003ATRPBF]] (3 units) pin 6 (Vsw) through NEC/TOKIN proadlizers | ||

|- | |- | ||

| | | data-sort-value="0E17" | E17 || {{cellcolors|#333|#fff}} GND || GND || {{pin}} || data-sort-value="ZGND" {{cellcolors||#888}} Ground | ||

|- | |- | ||

| | | data-sort-value="0E18" | E18 || {{cellcolors|#f93|#fff}} VDD || +1.0V_BE_VDDC || {{pin}} || data-sort-value="Z1.0V" | Connected to [[Regulators#iPowIR_IP2003ATRPBF_.2840A_Synchronous_Buck_Multiphase_Optimized_LGA_Power_Block.29|iPowIR IP2003ATRPBF]] (3 units) pin 6 (Vsw) through NEC/TOKIN proadlizers | ||

|- | |- | ||

| | | data-sort-value="0E19" | E19 || {{cellcolors|#333|#fff}} GND || GND || {{pin}} || data-sort-value="ZGND" {{cellcolors||#888}} Ground | ||

|- | |- | ||

| | | data-sort-value="0E20" | E20 || {{cellcolors|#f93|#fff}} VDD || +1.0V_BE_VDDC || {{pin}} || data-sort-value="Z1.0V" | Connected to [[Regulators#iPowIR_IP2003ATRPBF_.2840A_Synchronous_Buck_Multiphase_Optimized_LGA_Power_Block.29|iPowIR IP2003ATRPBF]] (3 units) pin 6 (Vsw) through NEC/TOKIN proadlizers | ||

|- | |- | ||

| | | data-sort-value="0E21" | E21 || {{cellcolors|#333|#fff}} GND || GND || {{pin}} || data-sort-value="ZGND" {{cellcolors||#888}} Ground | ||

|- | |- | ||

|- | | data-sort-value="0E22" | E22 || {{cellcolors|#f93|#fff}} VDD || +1.0V_BE_VDDC || {{pin}} || data-sort-value="Z1.0V" | Connected to [[Regulators#iPowIR_IP2003ATRPBF_.2840A_Synchronous_Buck_Multiphase_Optimized_LGA_Power_Block.29|iPowIR IP2003ATRPBF]] (3 units) pin 6 (Vsw) through NEC/TOKIN proadlizers | ||

|- | |- | ||

| data-sort-value="0E23" | E23 || {{cellcolors|#333|#fff}} GND || GND || {{pin}} || data-sort-value="ZGND" {{cellcolors||#888}} Ground | |||

|- | |- | ||

| | | data-sort-value="0E24" | E24 || {{cellcolors|#f93|#fff}} VDD || +1.0V_BE_VDDC || {{pin}} || data-sort-value="Z1.0V" | Connected to [[Regulators#iPowIR_IP2003ATRPBF_.2840A_Synchronous_Buck_Multiphase_Optimized_LGA_Power_Block.29|iPowIR IP2003ATRPBF]] (3 units) pin 6 (Vsw) through NEC/TOKIN proadlizers | ||

|- | |- | ||

| | | data-sort-value="0E25" | E25 || {{cellcolors|#333|#fff}} GND || GND || {{pin}} || data-sort-value="ZGND" {{cellcolors||#888}} Ground | ||

|- | |- | ||

| | | data-sort-value="0E26" | E26 || {{cellcolors|#f93|#fff}} VDD || +1.0V_BE_VDDC || {{pin}} || data-sort-value="Z1.0V" | Connected to [[Regulators#iPowIR_IP2003ATRPBF_.2840A_Synchronous_Buck_Multiphase_Optimized_LGA_Power_Block.29|iPowIR IP2003ATRPBF]] (3 units) pin 6 (Vsw) through NEC/TOKIN proadlizers | ||

|- | |- | ||

| | | data-sort-value="0E27" | E27 || {{cellcolors|#333|#fff}} GND || GND || {{pin}} || data-sort-value="ZGND" {{cellcolors||#888}} Ground | ||

|- | |- | ||

| | | data-sort-value="0E28" | E28 || {{cellcolors|#f93|#fff}} VDD || +1.0V_BE_VDDC || {{pin}} || data-sort-value="Z1.0V" | Connected to [[Regulators#iPowIR_IP2003ATRPBF_.2840A_Synchronous_Buck_Multiphase_Optimized_LGA_Power_Block.29|iPowIR IP2003ATRPBF]] (3 units) pin 6 (Vsw) through NEC/TOKIN proadlizers | ||

|- | |- | ||

| | | data-sort-value="0E29" | E29 || {{cellcolors|#333|#fff}} GND || GND || {{pin}} || data-sort-value="ZGND" {{cellcolors||#888}} Ground | ||

|- | |- | ||

| | | data-sort-value="0E30" | E30 || {{cellcolors|#f93|#fff}} VDD || +1.0V_BE_VDDC || {{pin}} || data-sort-value="Z1.0V" | Connected to [[Regulators#iPowIR_IP2003ATRPBF_.2840A_Synchronous_Buck_Multiphase_Optimized_LGA_Power_Block.29|iPowIR IP2003ATRPBF]] (3 units) pin 6 (Vsw) through NEC/TOKIN proadlizers | ||

|- | |- | ||

| | | data-sort-value="0E31" | E31 || {{cellcolors|#333|#fff}} GND || GND || {{pin}} || data-sort-value="ZGND" {{cellcolors||#888}} Ground | ||

|- | |- | ||

| | | data-sort-value="0E32" | E32 || {{cellcolors|#f93|#fff}} VDD || +1.0V_BE_VDDC || {{pin}} || data-sort-value="Z1.0V" | Connected to [[Regulators#iPowIR_IP2003ATRPBF_.2840A_Synchronous_Buck_Multiphase_Optimized_LGA_Power_Block.29|iPowIR IP2003ATRPBF]] (3 units) pin 6 (Vsw) through NEC/TOKIN proadlizers | ||

|- | |- | ||

| | | data-sort-value="0E33" | E33 || {{cellcolors|#333|#fff}} GND || GND || {{pin}} || data-sort-value="ZGND" {{cellcolors||#888}} Ground | ||

|- | |- | ||

| | | data-sort-value="0E34" | E34 || {{cellcolors|#c33|#fff}} TX0_VDDA || +1.5V_BE_RC_VDDA || {{pin}} || data-sort-value="Z1.5V" | Connected to [https://www.digikey.com/en/products/detail/vishay-siliconix/SI4866DY-T1-E3/2622290 Vishay Siliconix SI4866DY-T1-E3] pins 1,2,3 through RRAC filters | ||

|- | |- | ||

| | | data-sort-value="0E35" | E35 || RX0_RXP7 || BE_RX0_RXP7 || {{pini}} || Connected to [[RSX]] pad <abbr title="Unknown">UNK</abbr> ([[Template:RSX pad layout 41x41|41x41 layout]]) | ||

|- | |- | ||

| | | data-sort-value="0E36" | E36 || RX0_RXN7 || BE_RX0_RXN7 || {{pini}} || Connected to [[RSX]] pad <abbr title="Unknown">UNK</abbr> ([[Template:RSX pad layout 41x41|41x41 layout]]) | ||

|- | |- | ||

| | | data-sort-value="0E37" | E37 || {{cellcolors|#d53|#fff}} RC_VDDIO || +1.2V_YC_RC_VDDIO || {{pin}} || data-sort-value="Z1.2V_YC" | Connected to [https://www.digikey.com/en/products/detail/vishay-siliconix/SUD40N02-08-E3/2623039 Vishay Siliconix SUD40N02-08-E3] pin 3 | ||

|- | |- | ||

| | | data-sort-value="0E38" | E38 || TX0_TXN7 || BE_TX0_TXN7 || {{pino}} || Connected to [[RSX]] pad <abbr title="Unknown">UNK</abbr> ([[Template:RSX pad layout 41x41|41x41 layout]]) | ||

|- | |- | ||

| | | data-sort-value="0E39" | E39 || TX0_TXP7 || BE_TX0_TXP7 || {{pino}} || Connected to [[RSX]] pad <abbr title="Unknown">UNK</abbr> ([[Template:RSX pad layout 41x41|41x41 layout]]) | ||

|- | |- | ||

| | | data-sort-value="0E40" | E40 || data-sort-value="ZZZ" {{cellcolors|#eee|#888}} N/A || data-sort-value="ZZZ" {{cellcolors|#eee|#888}} N/A || data-sort-value="ZZZ" {{cellcolors|#eee|#888}} N/A || data-sort-value="ZZZ" {{cellcolors||#888}} Missing pad | ||

|- | |- | ||

| | | data-sort-value="0E41" | E41 || data-sort-value="ZZZ" {{cellcolors|#eee|#888}} N/A || data-sort-value="ZZZ" {{cellcolors|#eee|#888}} N/A || data-sort-value="ZZZ" {{cellcolors|#eee|#888}} N/A || data-sort-value="ZZZ" {{cellcolors||#888}} Missing pad | ||

|- | |- | ||

| | | data-sort-value="0E99" style="padding:0px" | || colspan="4" data-sort-value="ZZZZ" style="padding:0px" | | ||

|- | |- | ||

| | | data-sort-value="0F01" | F1 || {{cellcolors|#333|#fff}} GND || GND || {{pin}} || data-sort-value="ZGND" {{cellcolors||#888}} Ground | ||

|- | |- | ||

| | | data-sort-value="0F02" | F2 || data-sort-value="Y0_RQ00" {{cellcolors|#ff0}} Y0_RQ0 || data-sort-value="BE_Y0_RQ00" | BE_Y0_RQ0 || {{pino}} || Connected to [[RAM|XDR DRAM]] Y0_XDR0 (first chip), and Y0_XDR1 (second chip) pad C3. 12-bit request/command bus | ||

|- | |- | ||

| | | data-sort-value="0F03" | F3 || {{cellcolors|#333|#fff}} GND || GND || {{pin}} || data-sort-value="ZGND" {{cellcolors||#888}} Ground | ||

|- | |- | ||

| | | data-sort-value="0F04" | F4 || data-sort-value="Y0_RQ01" {{cellcolors|#ff0}} Y0_RQ1 || data-sort-value="BE_Y0_RQ01" | BE_Y0_RQ1 || {{pino}} || Connected to [[RAM|XDR DRAM]] Y0_XDR0 (first chip), and Y0_XDR1 (second chip) pad D13. 12-bit request/command bus | ||

|- | |- | ||

| | | data-sort-value="0F05" | F5 || {{cellcolors|#333|#fff}} GND || GND || {{pin}} || data-sort-value="ZGND" {{cellcolors||#888}} Ground | ||

|- | |- | ||

| | | data-sort-value="0F06" | F6 || Y0_RQ_SRD || BE_Y0_RQ_SRD || {{pini}} || Connected to [[RAM|XDR DRAM]] Y0_XDR0 (first chip) pad C16. Serial data in/out ? | ||

|- | |- | ||

| | | data-sort-value="0F07" | F7 || Y0_DQ1N_7 || data-sort-value="Y0_XDR1_DQN00" | Y0_XDR1_DQN0 || {{pino}} || Connected to [[RAM|XDR DRAM]] Y0_XDR1 (second chip) pad <abbr title="Unknown">UNK</abbr> | ||

|- | |- | ||

| | | data-sort-value="0F08" | F8 || Y0_DQ1N_0 || Y0_XDR1_DQN12 || {{pino}} || Connected to [[RAM|XDR DRAM]] Y0_XDR1 (second chip) pad <abbr title="Unknown">UNK</abbr> | ||

|- | |- | ||

| | | data-sort-value="0F09" | F9 || Y0_DQ0N_7 || data-sort-value="Y0_XDR1_DQN04" | Y0_XDR1_DQN4 || {{pino}} || Connected to [[RAM|XDR DRAM]] Y0_XDR1 (second chip) pad <abbr title="Unknown">UNK</abbr> | ||

|- | |- | ||

| | | data-sort-value="0F10" | F10 || Y0_DQ0N_2 || data-sort-value="Y0_XDR1_DQN08" | Y0_XDR1_DQN8 || {{pino}} || Connected to [[RAM|XDR DRAM]] Y0_XDR1 (second chip) pad <abbr title="Unknown">UNK</abbr> | ||

|- | |- | ||

| | | data-sort-value="0F11" | F11 || {{cellcolors|#333|#fff}} YC_SCAN_CLK4 || GND || {{pin}} || data-sort-value="ZGND" {{cellcolors||#888}} Ground | ||

|- | |- | ||

| | | data-sort-value="0F12" | F12 || {{cellcolors|#333|#fff}} GND || GND || {{pin}} || data-sort-value="ZGND" {{cellcolors||#888}} Ground | ||

|- | |- | ||

| | | data-sort-value="0F13" | F13 || {{cellcolors|#f93|#fff}} VDD || +1.0V_BE_VDDC || {{pin}} || data-sort-value="Z1.0V" | Connected to [[Regulators#iPowIR_IP2003ATRPBF_.2840A_Synchronous_Buck_Multiphase_Optimized_LGA_Power_Block.29|iPowIR IP2003ATRPBF]] (3 units) pin 6 (Vsw) through NEC/TOKIN proadlizers | ||

|- | |- | ||

| | | data-sort-value="0F14" | F14 || {{cellcolors|#333|#fff}} GND || GND || {{pin}} || data-sort-value="ZGND" {{cellcolors||#888}} Ground | ||

|- | |- | ||

| | | data-sort-value="0F15" | F15 || {{cellcolors|#f93|#fff}} VDD || +1.0V_BE_VDDC || {{pin}} || data-sort-value="Z1.0V" | Connected to [[Regulators#iPowIR_IP2003ATRPBF_.2840A_Synchronous_Buck_Multiphase_Optimized_LGA_Power_Block.29|iPowIR IP2003ATRPBF]] (3 units) pin 6 (Vsw) through NEC/TOKIN proadlizers | ||

|- | |- | ||

| | | data-sort-value="0F16" | F16 || {{cellcolors|#333|#fff}} GND || GND || {{pin}} || data-sort-value="ZGND" {{cellcolors||#888}} Ground | ||

|- | |- | ||

| | | data-sort-value="0F17" | F17 || {{cellcolors|#f93|#fff}} VDD || +1.0V_BE_VDDC || {{pin}} || data-sort-value="Z1.0V" | Connected to [[Regulators#iPowIR_IP2003ATRPBF_.2840A_Synchronous_Buck_Multiphase_Optimized_LGA_Power_Block.29|iPowIR IP2003ATRPBF]] (3 units) pin 6 (Vsw) through NEC/TOKIN proadlizers | ||

|- | |- | ||

| | | data-sort-value="0F18" | F18 || {{cellcolors|#333|#fff}} GND || GND || {{pin}} || data-sort-value="ZGND" {{cellcolors||#888}} Ground | ||

|- | |- | ||

| | | data-sort-value="0F19" | F19 || {{cellcolors|#f93|#fff}} VDD || +1.0V_BE_VDDC || {{pin}} || data-sort-value="Z1.0V" | Connected to [[Regulators#iPowIR_IP2003ATRPBF_.2840A_Synchronous_Buck_Multiphase_Optimized_LGA_Power_Block.29|iPowIR IP2003ATRPBF]] (3 units) pin 6 (Vsw) through NEC/TOKIN proadlizers | ||

|- | |- | ||

| | | data-sort-value="0F20" | F20 || {{cellcolors|#333|#fff}} GND || GND || {{pin}} || data-sort-value="ZGND" {{cellcolors||#888}} Ground | ||

|- | |- | ||

|- | | data-sort-value="0F21" | F21 || {{cellcolors|#f93|#fff}} VDD || +1.0V_BE_VDDC || {{pin}} || data-sort-value="Z1.0V" | Connected to [[Regulators#iPowIR_IP2003ATRPBF_.2840A_Synchronous_Buck_Multiphase_Optimized_LGA_Power_Block.29|iPowIR IP2003ATRPBF]] (3 units) pin 6 (Vsw) through NEC/TOKIN proadlizers | ||

|- | |- | ||

| data-sort-value="0F22" | F22 || {{cellcolors|#333|#fff}} GND || GND || {{pin}} || data-sort-value="ZGND" {{cellcolors||#888}} Ground | |||

|- | |- | ||

| | | data-sort-value="0F23" | F23 || {{cellcolors|#f93|#fff}} VDD || +1.0V_BE_VDDC || {{pin}} || data-sort-value="Z1.0V" | Connected to [[Regulators#iPowIR_IP2003ATRPBF_.2840A_Synchronous_Buck_Multiphase_Optimized_LGA_Power_Block.29|iPowIR IP2003ATRPBF]] (3 units) pin 6 (Vsw) through NEC/TOKIN proadlizers | ||

|- | |- | ||

| | | data-sort-value="0F24" | F24 || {{cellcolors|#333|#fff}} GND || GND || {{pin}} || data-sort-value="ZGND" {{cellcolors||#888}} Ground | ||

|- | |- | ||

| | | data-sort-value="0F25" | F25 || {{cellcolors|#f93|#fff}} VDD || +1.0V_BE_VDDC || {{pin}} || data-sort-value="Z1.0V" | Connected to [[Regulators#iPowIR_IP2003ATRPBF_.2840A_Synchronous_Buck_Multiphase_Optimized_LGA_Power_Block.29|iPowIR IP2003ATRPBF]] (3 units) pin 6 (Vsw) through NEC/TOKIN proadlizers | ||

|- | |- | ||

| | | data-sort-value="0F26" | F26 || {{cellcolors|#333|#fff}} GND || GND || {{pin}} || data-sort-value="ZGND" {{cellcolors||#888}} Ground | ||

|- | |- | ||

| | | data-sort-value="0F27" | F27 || {{cellcolors|#f93|#fff}} VDD || +1.0V_BE_VDDC || {{pin}} || data-sort-value="Z1.0V" | Connected to [[Regulators#iPowIR_IP2003ATRPBF_.2840A_Synchronous_Buck_Multiphase_Optimized_LGA_Power_Block.29|iPowIR IP2003ATRPBF]] (3 units) pin 6 (Vsw) through NEC/TOKIN proadlizers | ||

|- | |- | ||

| | | data-sort-value="0F28" | F28 || {{cellcolors|#333|#fff}} GND || GND || {{pin}} || data-sort-value="ZGND" {{cellcolors||#888}} Ground | ||

|- | |- | ||

| | | data-sort-value="0F29" | F29 || {{cellcolors|#f93|#fff}} VDD || +1.0V_BE_VDDC || {{pin}} || data-sort-value="Z1.0V" | Connected to [[Regulators#iPowIR_IP2003ATRPBF_.2840A_Synchronous_Buck_Multiphase_Optimized_LGA_Power_Block.29|iPowIR IP2003ATRPBF]] (3 units) pin 6 (Vsw) through NEC/TOKIN proadlizers | ||

|- | |- | ||

| | | data-sort-value="0F30" | F30 || {{cellcolors|#333|#fff}} GND || GND || {{pin}} || data-sort-value="ZGND" {{cellcolors||#888}} Ground | ||

|- | |- | ||

| | | data-sort-value="0F31" | F31 || {{cellcolors|#f93|#fff}} VDD || +1.0V_BE_VDDC || {{pin}} || data-sort-value="Z1.0V" | Connected to [[Regulators#iPowIR_IP2003ATRPBF_.2840A_Synchronous_Buck_Multiphase_Optimized_LGA_Power_Block.29|iPowIR IP2003ATRPBF]] (3 units) pin 6 (Vsw) through NEC/TOKIN proadlizers | ||

|- | |- | ||

| | | data-sort-value="0F32" | F32 || {{cellcolors|#333|#fff}} GND || GND || {{pin}} || data-sort-value="ZGND" {{cellcolors||#888}} Ground | ||

|- | |- | ||

| | | data-sort-value="0F33" | F33 || {{cellcolors|#f93|#fff}} VDD || +1.0V_BE_VDDC || {{pin}} || data-sort-value="Z1.0V" | Connected to [[Regulators#iPowIR_IP2003ATRPBF_.2840A_Synchronous_Buck_Multiphase_Optimized_LGA_Power_Block.29|iPowIR IP2003ATRPBF]] (3 units) pin 6 (Vsw) through NEC/TOKIN proadlizers | ||

|- | |- | ||

| | | data-sort-value="0F34" | F34 || {{cellcolors|#c33|#fff}} RX0_VDDA || +1.5V_BE_RC_VDDA || {{pin}} || data-sort-value="Z1.5V" | Connected to [https://www.digikey.com/en/products/detail/vishay-siliconix/SI4866DY-T1-E3/2622290 Vishay Siliconix SI4866DY-T1-E3] pins 1,2,3 through RRAC filters | ||

|- | |- | ||

| | | data-sort-value="0F35" | F35 || RX0_RXP5 || BE_RX0_RXP5 || {{pini}} || Connected to [[RSX]] pad <abbr title="Unknown">UNK</abbr> ([[Template:RSX pad layout 41x41|41x41 layout]]) | ||

|- | |- | ||

| | | data-sort-value="0F36" | F36 || RX0_RXN5 || BE_RX0_RXN5 || {{pini}} || Connected to [[RSX]] pad <abbr title="Unknown">UNK</abbr> ([[Template:RSX pad layout 41x41|41x41 layout]]) | ||

|- | |- | ||

| | | data-sort-value="0F37" | F37 || {{cellcolors|#333|#fff}} GND || GND || {{pin}} || data-sort-value="ZGND" {{cellcolors||#888}} Ground | ||

|- | |- | ||

| | | data-sort-value="0F38" | F38 || RX0_RXP4 || BE_RX0_RXP4 || {{pini}} || Connected to [[RSX]] pad <abbr title="Unknown">UNK</abbr> ([[Template:RSX pad layout 41x41|41x41 layout]]) | ||

|- | |- | ||

| | | data-sort-value="0F39" | F39 || RX0_RXN4 || BE_RX0_RXN4 || {{pini}} || Connected to [[RSX]] pad <abbr title="Unknown">UNK</abbr> ([[Template:RSX pad layout 41x41|41x41 layout]]) | ||

|- | |- | ||

| | | data-sort-value="0F40" | F40 || RX0_RXP6 || BE_RX0_RXP6 || {{pini}} || Connected to [[RSX]] pad <abbr title="Unknown">UNK</abbr> ([[Template:RSX pad layout 41x41|41x41 layout]]) | ||

|- | |- | ||

| | | data-sort-value="0F41" | F41 || RX0_RXN6 || BE_RX0_RXN6 || {{pini}} || Connected to [[RSX]] pad <abbr title="Unknown">UNK</abbr> ([[Template:RSX pad layout 41x41|41x41 layout]]) | ||

|- | |- | ||

| | | data-sort-value="0F99" style="padding:0px" | || colspan="4" data-sort-value="ZZZZ" style="padding:0px" | | ||

|- | |- | ||

| | | data-sort-value="0G01" | G1 || data-sort-value="Y0_RQ03" {{cellcolors|#ff0}} Y0_RQ3 || data-sort-value="BE_Y0_RQ03" | BE_Y0_RQ3 || {{pino}} || Connected to [[RAM|XDR DRAM]] Y0_XDR0 (first chip), and Y0_XDR1 (second chip) pad D4. 12-bit request/command bus | ||

|- | |- | ||

| | | data-sort-value="0G02" | G2 || {{cellcolors|#333|#fff}} GND || GND || {{pin}} || data-sort-value="ZGND" {{cellcolors||#888}} Ground | ||

|- | |- | ||

| | | data-sort-value="0G03" | G3 || data-sort-value="Y0_RQ05" {{cellcolors|#ff0}} Y0_RQ5 || data-sort-value="BE_Y0_RQ05" | BE_Y0_RQ5 || {{pino}} || Connected to [[RAM|XDR DRAM]] Y0_XDR0 (first chip), and Y0_XDR1 (second chip) pad E14. 12-bit request/command bus | ||

|- | |- | ||

| | | data-sort-value="0G04" | G4 || {{cellcolors|#333|#fff}} GND || GND || {{pin}} || data-sort-value="ZGND" {{cellcolors||#888}} Ground | ||

|- | |- | ||

| | | data-sort-value="0G05" | G5 || data-sort-value="Y0_RQ02" {{cellcolors|#ff0}} Y0_RQ2 || data-sort-value="BE_Y0_RQ02" | BE_Y0_RQ2 || {{pino}} || Connected to [[RAM|XDR DRAM]] Y0_XDR0 (first chip), and Y0_XDR1 (second chip) pad D14. 12-bit request/command bus | ||

|- | |- | ||

| | | data-sort-value="0G06" | G6 || {{cellcolors|#333|#fff}} GND || GND || {{pin}} || data-sort-value="ZGND" {{cellcolors||#888}} Ground | ||

|- | |- | ||

| | | data-sort-value="0G07" | G7 || Y0_DQ1_7 || data-sort-value="Y0_XDR1_DQ00" | Y0_XDR1_DQ0 || {{pino}} || Connected to [[RAM|XDR DRAM]] Y0_XDR1 (second chip) pad <abbr title="Unknown">UNK</abbr> | ||

|- | |- | ||

| | | data-sort-value="0G08" | G8 || Y0_DQ1_0 || Y0_XDR1_DQ12 || {{pino}} || Connected to [[RAM|XDR DRAM]] Y0_XDR1 (second chip) pad <abbr title="Unknown">UNK</abbr> | ||

|- | |- | ||

| | | data-sort-value="0G09" | G9 || Y0_DQ0_7 || data-sort-value="Y0_XDR1_DQ04" | Y0_XDR1_DQ4 || {{pino}} || Connected to [[RAM|XDR DRAM]] Y0_XDR1 (second chip) pad <abbr title="Unknown">UNK</abbr> | ||

|- | |- | ||

| | | data-sort-value="0G10" | G10 || Y0_DQ0_2 || data-sort-value="Y0_XDR1_DQ08" | Y0_XDR1_DQ8 || {{pino}} || Connected to [[RAM|XDR DRAM]] Y0_XDR1 (second chip) pad <abbr title="Unknown">UNK</abbr> | ||

|- | |- | ||

| | | data-sort-value="0G11" | G11 || {{cellcolors|#333|#fff}} YC_SCAN_CLK3 || GND || {{pin}} || data-sort-value="ZGND" {{cellcolors||#888}} Ground | ||

|- | |- | ||

| | | data-sort-value="0G12" | G12 || {{cellcolors|#f93|#fff}} VDD || +1.0V_BE_VDDC || {{pin}} || data-sort-value="Z1.0V" | Connected to [[Regulators#iPowIR_IP2003ATRPBF_.2840A_Synchronous_Buck_Multiphase_Optimized_LGA_Power_Block.29|iPowIR IP2003ATRPBF]] (3 units) pin 6 (Vsw) through NEC/TOKIN proadlizers | ||

|- | |- | ||

| | | data-sort-value="0G13" | G13 || {{cellcolors|#333|#fff}} GND || GND || {{pin}} || data-sort-value="ZGND" {{cellcolors||#888}} Ground | ||

|- | |- | ||

| | | data-sort-value="0G14" | G14 || {{cellcolors|#f93|#fff}} VDD || +1.0V_BE_VDDC || {{pin}} || data-sort-value="Z1.0V" | Connected to [[Regulators#iPowIR_IP2003ATRPBF_.2840A_Synchronous_Buck_Multiphase_Optimized_LGA_Power_Block.29|iPowIR IP2003ATRPBF]] (3 units) pin 6 (Vsw) through NEC/TOKIN proadlizers | ||

|- | |- | ||

| | | data-sort-value="0G15" | G15 || {{cellcolors|#333|#fff}} GND || GND || {{pin}} || data-sort-value="ZGND" {{cellcolors||#888}} Ground | ||

|- | |- | ||

| | | data-sort-value="0G16" | G16 || {{cellcolors|#f93|#fff}} VDD || +1.0V_BE_VDDC || {{pin}} || data-sort-value="Z1.0V" | Connected to [[Regulators#iPowIR_IP2003ATRPBF_.2840A_Synchronous_Buck_Multiphase_Optimized_LGA_Power_Block.29|iPowIR IP2003ATRPBF]] (3 units) pin 6 (Vsw) through NEC/TOKIN proadlizers | ||

|- | |- | ||

| | | data-sort-value="0G17" | G17 || {{cellcolors|#333|#fff}} GND || GND || {{pin}} || data-sort-value="ZGND" {{cellcolors||#888}} Ground | ||

|- | |- | ||

| | | data-sort-value="0G18" | G18 || {{cellcolors|#f93|#fff}} VDD || +1.0V_BE_VDDC || {{pin}} || data-sort-value="Z1.0V" | Connected to [[Regulators#iPowIR_IP2003ATRPBF_.2840A_Synchronous_Buck_Multiphase_Optimized_LGA_Power_Block.29|iPowIR IP2003ATRPBF]] (3 units) pin 6 (Vsw) through NEC/TOKIN proadlizers | ||

|- | |- | ||

| | | data-sort-value="0G19" | G19 || {{cellcolors|#333|#fff}} GND || GND || {{pin}} || data-sort-value="ZGND" {{cellcolors||#888}} Ground | ||

|- | |- | ||

| | | data-sort-value="0G20" | G20 || {{cellcolors|#f93|#fff}} VDD || +1.0V_BE_VDDC || {{pin}} || data-sort-value="Z1.0V" | Connected to [[Regulators#iPowIR_IP2003ATRPBF_.2840A_Synchronous_Buck_Multiphase_Optimized_LGA_Power_Block.29|iPowIR IP2003ATRPBF]] (3 units) pin 6 (Vsw) through NEC/TOKIN proadlizers | ||

|- | |- | ||

| | | data-sort-value="0G21" | G21 || {{cellcolors|#333|#fff}} GND || GND || {{pin}} || data-sort-value="ZGND" {{cellcolors||#888}} Ground | ||

|- | |- | ||

|- | | data-sort-value="0G22" | G22 || {{cellcolors|#f93|#fff}} VDD || +1.0V_BE_VDDC || {{pin}} || data-sort-value="Z1.0V" | Connected to [[Regulators#iPowIR_IP2003ATRPBF_.2840A_Synchronous_Buck_Multiphase_Optimized_LGA_Power_Block.29|iPowIR IP2003ATRPBF]] (3 units) pin 6 (Vsw) through NEC/TOKIN proadlizers | ||

|- | |- | ||

| data-sort-value="0G23" | G23 || {{cellcolors|#333|#fff}} GND || GND || {{pin}} || data-sort-value="ZGND" {{cellcolors||#888}} Ground | |||

|- | |- | ||

| | | data-sort-value="0G24" | G24 || {{cellcolors|#f93|#fff}} VDD || +1.0V_BE_VDDC || {{pin}} || data-sort-value="Z1.0V" | Connected to [[Regulators#iPowIR_IP2003ATRPBF_.2840A_Synchronous_Buck_Multiphase_Optimized_LGA_Power_Block.29|iPowIR IP2003ATRPBF]] (3 units) pin 6 (Vsw) through NEC/TOKIN proadlizers | ||

|- | |- | ||

| | | data-sort-value="0G25" | G25 || {{cellcolors|#333|#fff}} GND || GND || {{pin}} || data-sort-value="ZGND" {{cellcolors||#888}} Ground | ||

|- | |- | ||

| | | data-sort-value="0G26" | G26 || {{cellcolors|#f93|#fff}} VDD || +1.0V_BE_VDDC || {{pin}} || data-sort-value="Z1.0V" | Connected to [[Regulators#iPowIR_IP2003ATRPBF_.2840A_Synchronous_Buck_Multiphase_Optimized_LGA_Power_Block.29|iPowIR IP2003ATRPBF]] (3 units) pin 6 (Vsw) through NEC/TOKIN proadlizers | ||

|- | |- | ||

| | | data-sort-value="0G27" | G27 || {{cellcolors|#333|#fff}} GND || GND || {{pin}} || data-sort-value="ZGND" {{cellcolors||#888}} Ground | ||

|- | |- | ||

| | | data-sort-value="0G28" | G28 || {{cellcolors|#f93|#fff}} VDD || +1.0V_BE_VDDC || {{pin}} || data-sort-value="Z1.0V" | Connected to [[Regulators#iPowIR_IP2003ATRPBF_.2840A_Synchronous_Buck_Multiphase_Optimized_LGA_Power_Block.29|iPowIR IP2003ATRPBF]] (3 units) pin 6 (Vsw) through NEC/TOKIN proadlizers | ||

|- | |- | ||

| | | data-sort-value="0G29" | G29 || {{cellcolors|#333|#fff}} GND || GND || {{pin}} || data-sort-value="ZGND" {{cellcolors||#888}} Ground | ||

|- | |- | ||

| | | data-sort-value="0G30" | G30 || {{cellcolors|#f93|#fff}} VDD || +1.0V_BE_VDDC || {{pin}} || data-sort-value="Z1.0V" | Connected to [[Regulators#iPowIR_IP2003ATRPBF_.2840A_Synchronous_Buck_Multiphase_Optimized_LGA_Power_Block.29|iPowIR IP2003ATRPBF]] (3 units) pin 6 (Vsw) through NEC/TOKIN proadlizers | ||

|- | |- | ||

| | | data-sort-value="0G31" | G31 || {{cellcolors|#333|#fff}} GND || GND || {{pin}} || data-sort-value="ZGND" {{cellcolors||#888}} Ground | ||

|- | |- | ||

| | | data-sort-value="0G32" | G32 || {{cellcolors|#f93|#fff}} VDD || +1.0V_BE_VDDC || {{pin}} || data-sort-value="Z1.0V" | Connected to [[Regulators#iPowIR_IP2003ATRPBF_.2840A_Synchronous_Buck_Multiphase_Optimized_LGA_Power_Block.29|iPowIR IP2003ATRPBF]] (3 units) pin 6 (Vsw) through NEC/TOKIN proadlizers | ||

|- | |- | ||

| | | data-sort-value="0G33" | G33 || {{cellcolors|#333|#fff}} GND || GND || {{pin}} || data-sort-value="ZGND" {{cellcolors||#888}} Ground | ||

|- | |- | ||

| | | data-sort-value="0G34" | G34 || {{cellcolors|#333|#fff}} RX0_GNDA || GND || {{pin}} || data-sort-value="ZGND" {{cellcolors||#888}} Ground | ||

|- | |- | ||

| | | data-sort-value="0G35" | G35 || RX0_RXP3 || BE_RX0_RXP3 || {{pini}} || Connected to [[RSX]] pad <abbr title="Unknown">UNK</abbr> ([[Template:RSX pad layout 41x41|41x41 layout]]) | ||

|- | |- | ||

| | | data-sort-value="0G36" | G36 || RX0_RXN3 || BE_RX0_RXN3 || {{pini}} || Connected to [[RSX]] pad <abbr title="Unknown">UNK</abbr> ([[Template:RSX pad layout 41x41|41x41 layout]]) | ||

|- | |- | ||

| | | data-sort-value="0G37" | G37 || {{cellcolors|#333|#fff}} GND || GND || {{pin}} || data-sort-value="ZGND" {{cellcolors||#888}} Ground | ||

|- | |- | ||

| | | data-sort-value="0G38" | G38 || RX0_RXCLKP || BE_RX0_RXCLKP || {{pini}} || Connected to [[RSX]] pad <abbr title="Unknown">UNK</abbr> ([[Template:RSX pad layout 41x41|41x41 layout]]) | ||

|- | |- | ||

| | | data-sort-value="0G39" | G39 || RX0_RXCLKN || BE_RX0_RXCLKN || {{pini}} || Connected to [[RSX]] pad <abbr title="Unknown">UNK</abbr> ([[Template:RSX pad layout 41x41|41x41 layout]]) | ||

|- | |- | ||

| | | data-sort-value="0G40" | G40 || data-sort-value="ZZZ" {{cellcolors|#eee|#888}} N/A || data-sort-value="ZZZ" {{cellcolors|#eee|#888}} N/A || data-sort-value="ZZZ" {{cellcolors|#eee|#888}} N/A || data-sort-value="ZZZ" {{cellcolors||#888}} Missing pad | ||

|- | |- | ||

| | | data-sort-value="0G41" | G41 || data-sort-value="ZZZ" {{cellcolors|#eee|#888}} N/A || data-sort-value="ZZZ" {{cellcolors|#eee|#888}} N/A || data-sort-value="ZZZ" {{cellcolors|#eee|#888}} N/A || data-sort-value="ZZZ" {{cellcolors||#888}} Missing pad | ||

|- | |- | ||

| | | data-sort-value="0G99" style="padding:0px" | || colspan="4" data-sort-value="ZZZZ" style="padding:0px" | | ||

|- | |- | ||

| | | data-sort-value="0H01" | H1 || {{cellcolors|#333|#fff}} GND || GND || {{pin}} || data-sort-value="ZGND" {{cellcolors||#888}} Ground | ||

|- | |- | ||

| | | data-sort-value="0H02" | H2 || data-sort-value="Y0_RQ04" {{cellcolors|#ff0}} Y0_RQ4 || data-sort-value="BE_Y0_RQ04" | BE_Y0_RQ4 || {{pino}} || Connected to [[RAM|XDR DRAM]] Y0_XDR0 (first chip), and Y0_XDR1 (second chip) pad D3. 12-bit request/command bus | ||

|- | |- | ||

| | | data-sort-value="0H03" | H3 || {{cellcolors|#333|#fff}} GND || GND || {{pin}} || data-sort-value="ZGND" {{cellcolors||#888}} Ground | ||

|- | |- | ||

| | | data-sort-value="0H04" | H4 || data-sort-value="Y0_RQ06" {{cellcolors|#ff0}} Y0_RQ6 || data-sort-value="BE_Y0_RQ06" | BE_Y0_RQ6 || {{pino}} || Connected to [[RAM|XDR DRAM]] Y0_XDR0 (first chip), and Y0_XDR1 (second chip) pad G14. 12-bit request/command bus | ||

|- | |- | ||

| | | data-sort-value="0H05" | H5 || {{cellcolors|#333|#fff}} GND || GND || {{pin}} || data-sort-value="ZGND" {{cellcolors||#888}} Ground | ||

|- | |- | ||

| | | data-sort-value="0H06" | H6 || Y0_RQ_VREF || BE_Y0_RQ_VREF || {{pini}} || Connected to [[RAM|XDR DRAM]] Y0_XDR0 (first chip), and Y0_XDR1 (second chip) power circuit | ||

|- | |- | ||

| | | data-sort-value="0H07" | H7 || {{cellcolors|#333|#fff}} GND || GND || {{pin}} || data-sort-value="ZGND" {{cellcolors||#888}} Ground | ||

|- | |- | ||

| | | data-sort-value="0H08" | H8 || {{cellcolors|#c33|#fff}} Y0_DQ0_VDDA || +1.5V_BE_YC_VDDA || {{pin}} || data-sort-value="Z1.5V" | Connected to [https://www.digikey.com/en/products/detail/vishay-siliconix/SI4866DY-T1-E3/2622290 Vishay Siliconix SI4866DY-T1-E3] pins 1,2,3 through XIO filters | ||

|- | |- | ||

| | | data-sort-value="0H09" | H9 || {{cellcolors|#333|#fff}} Y0_DQ0_GNDA || GND || {{pin}} || data-sort-value="ZGND" {{cellcolors||#888}} Ground | ||

|- | |- | ||

| | | data-sort-value="0H10" | H10 || {{cellcolors|#333|#fff}} GND || GND || {{pin}} || data-sort-value="ZGND" {{cellcolors||#888}} Ground | ||

|- | |- | ||

| | | data-sort-value="0H11" | H11 || {{cellcolors|#333|#fff}} YC_SCAN_CLK2 || GND || {{pin}} || data-sort-value="ZGND" {{cellcolors||#888}} Ground | ||

|- | |- | ||

| | | data-sort-value="0H12" | H12 || {{cellcolors|#333|#fff}} GND || GND || {{pin}} || data-sort-value="ZGND" {{cellcolors||#888}} Ground | ||

|- | |- | ||

| | | data-sort-value="0H13" | H13 || {{cellcolors|#f93|#fff}} VDD || +1.0V_BE_VDDC || {{pin}} || data-sort-value="Z1.0V" | Connected to [[Regulators#iPowIR_IP2003ATRPBF_.2840A_Synchronous_Buck_Multiphase_Optimized_LGA_Power_Block.29|iPowIR IP2003ATRPBF]] (3 units) pin 6 (Vsw) through NEC/TOKIN proadlizers | ||

|- | |- | ||

| | | data-sort-value="0H14" | H14 || {{cellcolors|#333|#fff}} GND || GND || {{pin}} || data-sort-value="ZGND" {{cellcolors||#888}} Ground | ||

|- | |- | ||

| | | data-sort-value="0H15" | H15 || {{cellcolors|#f93|#fff}} VDD || +1.0V_BE_VDDC || {{pin}} || data-sort-value="Z1.0V" | Connected to [[Regulators#iPowIR_IP2003ATRPBF_.2840A_Synchronous_Buck_Multiphase_Optimized_LGA_Power_Block.29|iPowIR IP2003ATRPBF]] (3 units) pin 6 (Vsw) through NEC/TOKIN proadlizers | ||

|- | |- | ||

| | | data-sort-value="0H16" | H16 || {{cellcolors|#333|#fff}} GND || GND || {{pin}} || data-sort-value="ZGND" {{cellcolors||#888}} Ground | ||

|- | |- | ||

| | | data-sort-value="0H17" | H17 || {{cellcolors|#f93|#fff}} VDD || +1.0V_BE_VDDC || {{pin}} || data-sort-value="Z1.0V" | Connected to [[Regulators#iPowIR_IP2003ATRPBF_.2840A_Synchronous_Buck_Multiphase_Optimized_LGA_Power_Block.29|iPowIR IP2003ATRPBF]] (3 units) pin 6 (Vsw) through NEC/TOKIN proadlizers | ||

|- | |- | ||

| | | data-sort-value="0H18" | H18 || {{cellcolors|#333|#fff}} GND || GND || {{pin}} || data-sort-value="ZGND" {{cellcolors||#888}} Ground | ||

|- | |- | ||

| | | data-sort-value="0H19" | H19 || {{cellcolors|#f93|#fff}} VDD || +1.0V_BE_VDDC || {{pin}} || data-sort-value="Z1.0V" | Connected to [[Regulators#iPowIR_IP2003ATRPBF_.2840A_Synchronous_Buck_Multiphase_Optimized_LGA_Power_Block.29|iPowIR IP2003ATRPBF]] (3 units) pin 6 (Vsw) through NEC/TOKIN proadlizers | ||

|- | |- | ||

| | | data-sort-value="0H20" | H20 || {{cellcolors|#333|#fff}} GND || GND || {{pin}} || data-sort-value="ZGND" {{cellcolors||#888}} Ground | ||

|- | |- | ||

|- | | data-sort-value="0H21" | H21 || {{cellcolors|#f93|#fff}} VDD || +1.0V_BE_VDDC || {{pin}} || data-sort-value="Z1.0V" | Connected to [[Regulators#iPowIR_IP2003ATRPBF_.2840A_Synchronous_Buck_Multiphase_Optimized_LGA_Power_Block.29|iPowIR IP2003ATRPBF]] (3 units) pin 6 (Vsw) through NEC/TOKIN proadlizers | ||

|- | |- | ||

| data-sort-value="0H22" | H22 || {{cellcolors|#333|#fff}} GND || GND || {{pin}} || data-sort-value="ZGND" {{cellcolors||#888}} Ground | |||

|- | |- | ||

| | | data-sort-value="0H23" | H23 || {{cellcolors|#f93|#fff}} VDD || +1.0V_BE_VDDC || {{pin}} || data-sort-value="Z1.0V" | Connected to [[Regulators#iPowIR_IP2003ATRPBF_.2840A_Synchronous_Buck_Multiphase_Optimized_LGA_Power_Block.29|iPowIR IP2003ATRPBF]] (3 units) pin 6 (Vsw) through NEC/TOKIN proadlizers | ||

|- | |- | ||

| | | data-sort-value="0H24" | H24 || {{cellcolors|#333|#fff}} GND || GND || {{pin}} || data-sort-value="ZGND" {{cellcolors||#888}} Ground | ||

|- | |- | ||

| | | data-sort-value="0H25" | H25 || {{cellcolors|#f93|#fff}} VDD || +1.0V_BE_VDDC || {{pin}} || data-sort-value="Z1.0V" | Connected to [[Regulators#iPowIR_IP2003ATRPBF_.2840A_Synchronous_Buck_Multiphase_Optimized_LGA_Power_Block.29|iPowIR IP2003ATRPBF]] (3 units) pin 6 (Vsw) through NEC/TOKIN proadlizers | ||

|- | |- | ||

| | | data-sort-value="0H26" | H26 || {{cellcolors|#333|#fff}} GND || GND || {{pin}} || data-sort-value="ZGND" {{cellcolors||#888}} Ground | ||

|- | |- | ||

| | | data-sort-value="0H27" | H27 || {{cellcolors|#f93|#fff}} VDD || +1.0V_BE_VDDC || {{pin}} || data-sort-value="Z1.0V" | Connected to [[Regulators#iPowIR_IP2003ATRPBF_.2840A_Synchronous_Buck_Multiphase_Optimized_LGA_Power_Block.29|iPowIR IP2003ATRPBF]] (3 units) pin 6 (Vsw) through NEC/TOKIN proadlizers | ||

|- | |- | ||

| | | data-sort-value="0H28" | H28 || {{cellcolors|#333|#fff}} GND || GND || {{pin}} || data-sort-value="ZGND" {{cellcolors||#888}} Ground | ||

|- | |- | ||

| | | data-sort-value="0H29" | H29 || {{cellcolors|#f93|#fff}} VDD || +1.0V_BE_VDDC || {{pin}} || data-sort-value="Z1.0V" | Connected to [[Regulators#iPowIR_IP2003ATRPBF_.2840A_Synchronous_Buck_Multiphase_Optimized_LGA_Power_Block.29|iPowIR IP2003ATRPBF]] (3 units) pin 6 (Vsw) through NEC/TOKIN proadlizers | ||

|- | |- | ||

| | | data-sort-value="0H30" | H30 || {{cellcolors|#333|#fff}} GND || GND || {{pin}} || data-sort-value="ZGND" {{cellcolors||#888}} Ground | ||

|- | |- | ||

| | | data-sort-value="0H31" | H31 || {{cellcolors|#f93|#fff}} VDD || +1.0V_BE_VDDC || {{pin}} || data-sort-value="Z1.0V" | Connected to [[Regulators#iPowIR_IP2003ATRPBF_.2840A_Synchronous_Buck_Multiphase_Optimized_LGA_Power_Block.29|iPowIR IP2003ATRPBF]] (3 units) pin 6 (Vsw) through NEC/TOKIN proadlizers | ||

|- | |- | ||

| | | data-sort-value="0H32" | H32 || {{cellcolors|#333|#fff}} GND || GND || {{pin}} || data-sort-value="ZGND" {{cellcolors||#888}} Ground | ||

|- | |- | ||

| | | data-sort-value="0H33" | H33 || {{cellcolors|#f93|#fff}} VDD || +1.0V_BE_VDDC || {{pin}} || data-sort-value="Z1.0V" | Connected to [[Regulators#iPowIR_IP2003ATRPBF_.2840A_Synchronous_Buck_Multiphase_Optimized_LGA_Power_Block.29|iPowIR IP2003ATRPBF]] (3 units) pin 6 (Vsw) through NEC/TOKIN proadlizers | ||

|- | |- | ||

| | | data-sort-value="0H34" | H34 || {{cellcolors|#333|#fff}} GND || GND || {{pin}} || data-sort-value="ZGND" {{cellcolors||#888}} Ground | ||

|- | |- | ||

| | | data-sort-value="0H35" | H35 || RX0_RXP1 || BE_RX0_RXP1 || {{pini}} || Connected to [[RSX]] pad <abbr title="Unknown">UNK</abbr> ([[Template:RSX pad layout 41x41|41x41 layout]]) | ||

|- | |- | ||

| | | data-sort-value="0H36" | H36 || RX0_RXN1 || BE_RX0_RXN1 || {{pini}} || Connected to [[RSX]] pad <abbr title="Unknown">UNK</abbr> ([[Template:RSX pad layout 41x41|41x41 layout]]) | ||