Template:CELL pad layout 65nm: Difference between revisions

Jump to navigation

Jump to search

No edit summary |

(Table style copyed from the 90nm table) |

||

| Line 7: | Line 7: | ||

{| class="wikitable mw-datatable sortable" style="width:100%; line-height:1em; font-size:0.9em" | {| class="wikitable mw-datatable sortable" style="width:100%; line-height:1em; font-size:0.9em" | ||

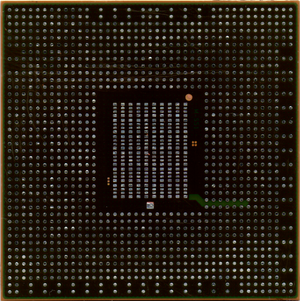

|+ {{captionlinks|CELL pad layout 65nm}} | |+ {{captionlinks|CELL pad layout 65nm}} | ||

! style=" | ! style="border-bottom:hidden; padding:2px" | Pad !! colspan="2" | Name !! style="border-bottom:hidden; padding:2px" | Type !! style="border-bottom:hidden" | Description | ||

|- | |- | ||

| | ! style="border-top:hidden; padding:0px; background-position:50%" | !! style="width:25px; min-width:25px; padding-right:0px" | Internal !! style="width:25px; min-width:25px; padding-right:0px" | External !! style="border-top:hidden; background-position:50%" | !! style="border-top:hidden; background-position:50%" | | ||

|- | |- | ||

| | | AV13 || SPI_SI/BE_SPI_DO || || {{pini}} || Connected to [[Syscon Hardware|Syscon]] pad N2 ([[Template:Syscon_pinout_BGA_200_pads|BGA 200 pads layout]]), or pin 80 ([[Template:Syscon_pinout_LQFP_128_pins|LQFP 128 pins layout]]) | ||

|- | |- | ||

| | | AV23 || THERMAL_OVERLOAD/SYS_THR_ALRT || || {{pino}} || Connected to [[Syscon Hardware|Syscon]] pad E9 ([[Template:Syscon_pinout_BGA_200_pads|BGA 200 pads layout]]), or pin <abbr title="Unknown>UNK</abbr> ([[Template:Syscon_pinout_LQFP_128_pins|LQFP 128 pins layout]]) through transistor | ||

|- | |- | ||

| | | AW13 || SPI_EN/BE_SPI_CS || || {{pini}} || Connected to [[Syscon Hardware|Syscon]] pad M2 ([[Template:Syscon_pinout_BGA_200_pads|BGA 200 pads layout]]), or pin 83 ([[Template:Syscon_pinout_LQFP_128_pins|LQFP 128 pins layout]]) | ||

|- | |- | ||

| | | AW18 || HARD_RESET/BE_RESET_AND || || {{pini}} || Connected to [[Syscon Hardware|Syscon]] pad P2 ([[Template:Syscon_pinout_BGA_200_pads|BGA 200 pads layout]]), or pin <abbr title="Unknown>UNK</abbr> ([[Template:Syscon_pinout_LQFP_128_pins|LQFP 128 pins layout]]) | ||

|- | |- | ||

| | | AY13 || SPI_CLK/BE_SPI_CLK || || {{pini}} || Connected to [[Syscon Hardware|Syscon]] pad N1 ([[Template:Syscon_pinout_BGA_200_pads|BGA 200 pads layout]]), or pin 82 ([[Template:Syscon_pinout_LQFP_128_pins|LQFP 128 pins layout]]) | ||

|- | |- | ||

| | | BA13 || SPI_SO/BE_SPI_DI || || {{pino}} || Connected to [[Syscon Hardware|Syscon]] pad M1 ([[Template:Syscon_pinout_BGA_200_pads|BGA 200 pads layout]]), or pin 81 ([[Template:Syscon_pinout_LQFP_128_pins|LQFP 128 pins layout]]) through 47 resistor | ||

|- | |- | ||

| BA19 || POWER_GOOD/BE_POWGOOD || | | BA17 || ATTENTION/BE_INT || || {{pino}} || Connected to [[Syscon Hardware|Syscon]] pad T2 ([[Template:Syscon_pinout_BGA_200_pads|BGA 200 pads layout]]), or pin 3 ([[Template:Syscon_pinout_LQFP_128_pins|LQFP 128 pins layout]]) | ||

|- | |||

| BA19 || POWER_GOOD/BE_POWGOOD || || {{pini}} || Connected to [[Syscon Hardware|Syscon]] pad P1 ([[Template:Syscon_pinout_BGA_200_pads|BGA 200 pads layout]]), or pin <abbr title="Unknown>UNK</abbr> ([[Template:Syscon_pinout_LQFP_128_pins|LQFP 128 pins layout]]) | |||

|} | |} | ||

</div> | </div> | ||

<noinclude>[[Category:Templates]]</noinclude> | <noinclude>[[Category:Templates]]</noinclude> | ||

Revision as of 03:53, 10 November 2022

| Name | ||||

|---|---|---|---|---|

| Internal | External | |||

| AV13 | SPI_SI/BE_SPI_DO | Connected to Syscon pad N2 (BGA 200 pads layout), or pin 80 (LQFP 128 pins layout) | ||

| AV23 | THERMAL_OVERLOAD/SYS_THR_ALRT | Connected to Syscon pad E9 (BGA 200 pads layout), or pin UNK (LQFP 128 pins layout) through transistor | ||

| AW13 | SPI_EN/BE_SPI_CS | Connected to Syscon pad M2 (BGA 200 pads layout), or pin 83 (LQFP 128 pins layout) | ||

| AW18 | HARD_RESET/BE_RESET_AND | Connected to Syscon pad P2 (BGA 200 pads layout), or pin UNK (LQFP 128 pins layout) | ||

| AY13 | SPI_CLK/BE_SPI_CLK | Connected to Syscon pad N1 (BGA 200 pads layout), or pin 82 (LQFP 128 pins layout) | ||

| BA13 | SPI_SO/BE_SPI_DI | Connected to Syscon pad M1 (BGA 200 pads layout), or pin 81 (LQFP 128 pins layout) through 47 resistor | ||

| BA17 | ATTENTION/BE_INT | Connected to Syscon pad T2 (BGA 200 pads layout), or pin 3 (LQFP 128 pins layout) | ||

| BA19 | POWER_GOOD/BE_POWGOOD | Connected to Syscon pad P1 (BGA 200 pads layout), or pin UNK (LQFP 128 pins layout) | ||